# GaN Power HEMT Tutorial: GaN Driving

**GANPOWER** INTERNATIONAL INC

Fred Yue Fu (傅玥) Co-founder and COO GaNPower International Inc.

### Contents

#### ➢ Session 1: GaN devices basics

#### ➢ Session 2: GaN Gate Driving

- ➢ Gate driving basics

- ➢ High dv/dt and di/dt issues

- ➢ Gate drivers and isolation

- Gate drive related power loss calculations

- Co-package and monolithic GaN IC

➢ Session 3: GaN Applications

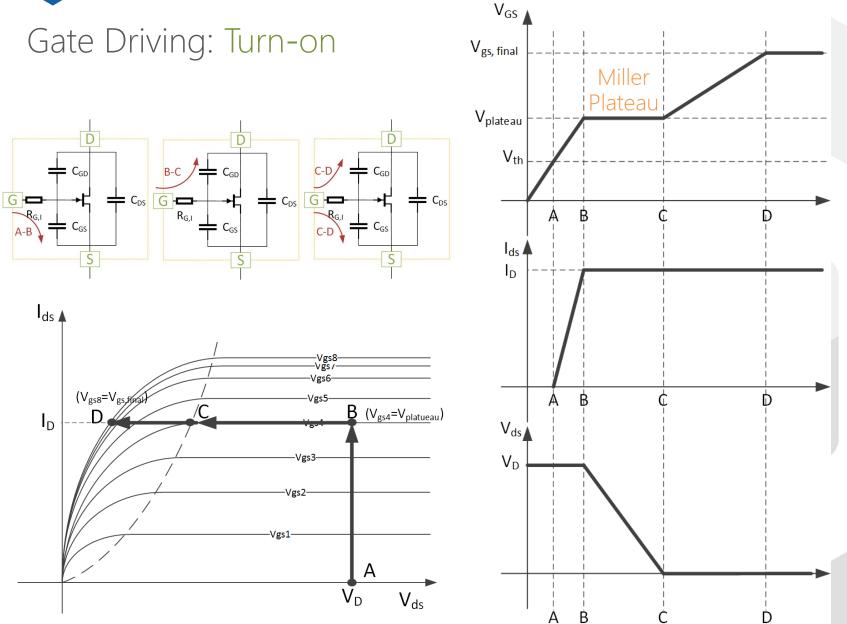

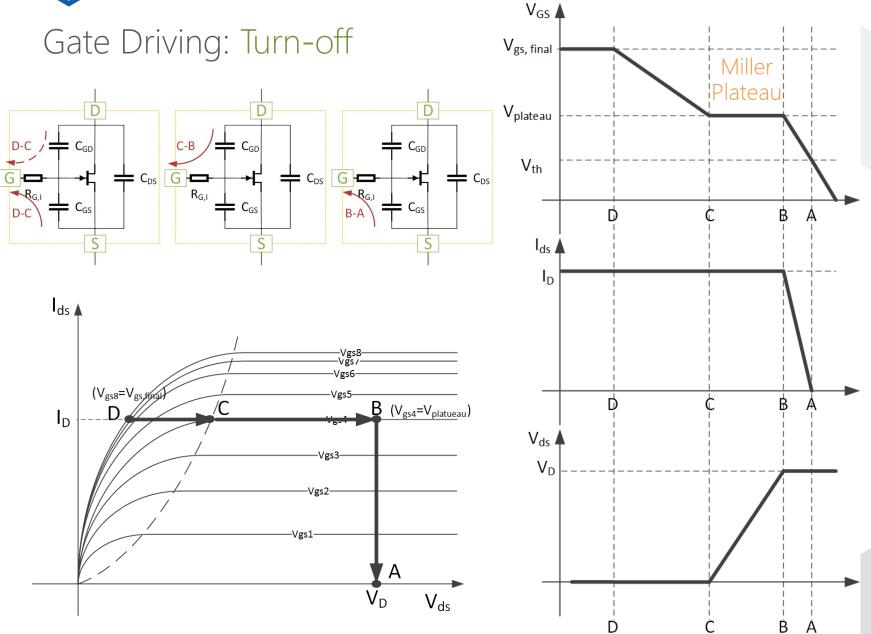

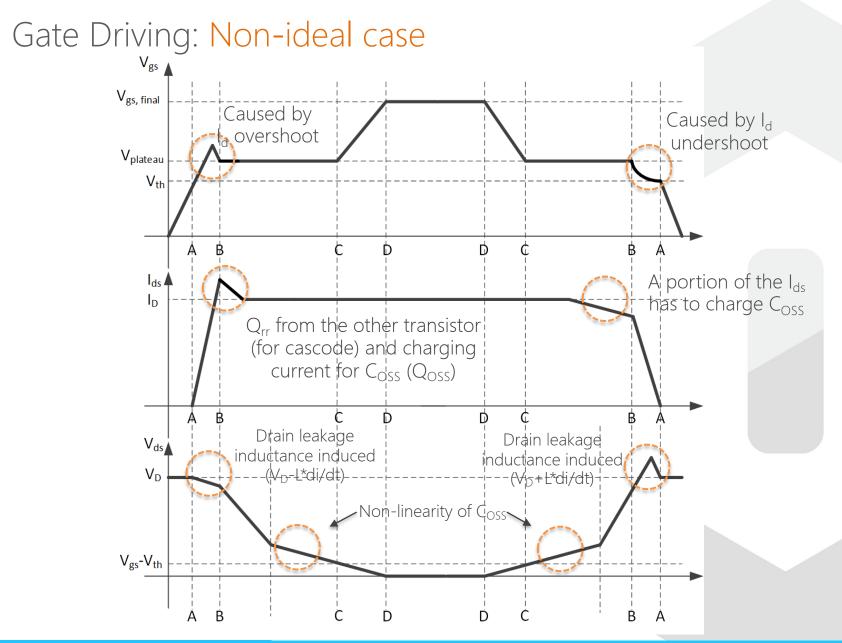

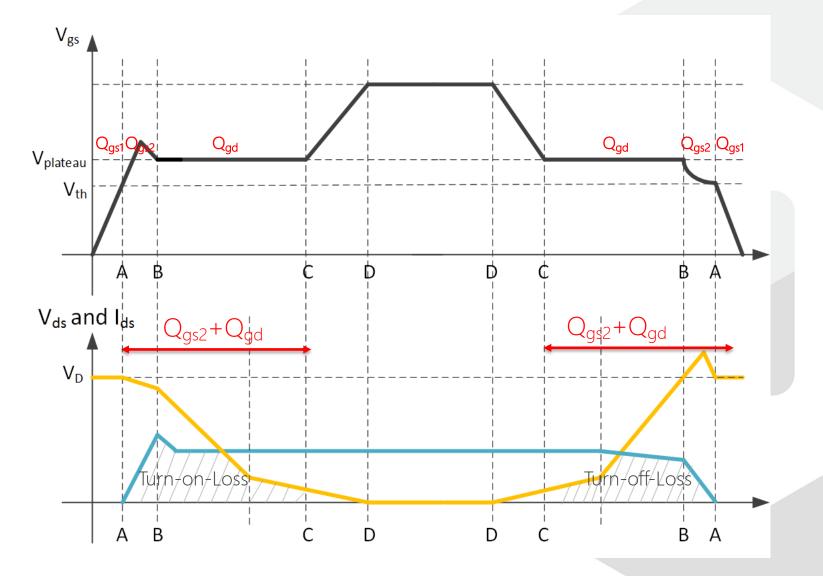

Gate Driving: Switching Loss

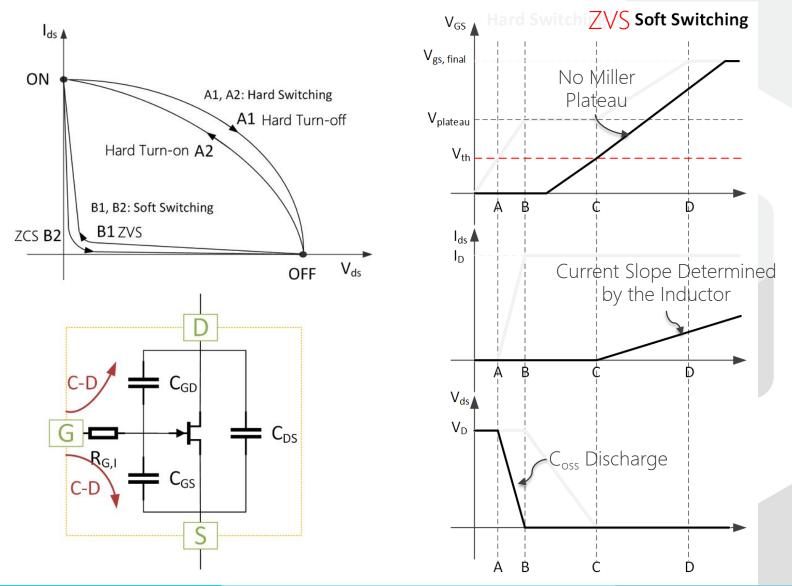

#### Gate Driving: Soft and Hard-switching Turning-on

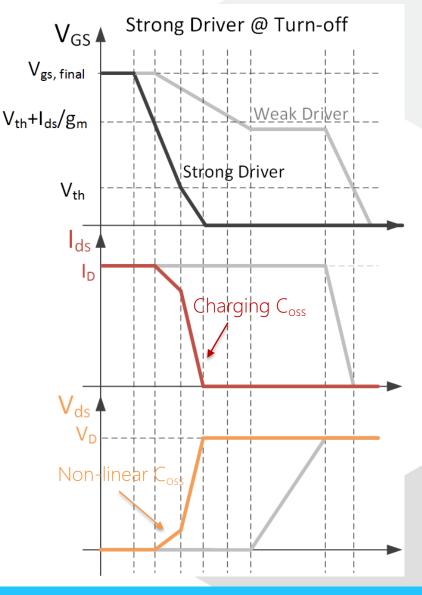

#### Gate Driving: Turning-off with Strong Driver

- ZVS provides soft-switching at turningon, but turning-off is still hard switching

- A strong driver increases switching speed, reduces switching time and switching losses

- For a strong driver turn-off, Miller plateau may not be observed. This is exactly what we have seen when switching GaN devices off

Ref: Wei Zhang, Mastering the art and fundamentals of high voltage gate driver; TI High Volt Interactive

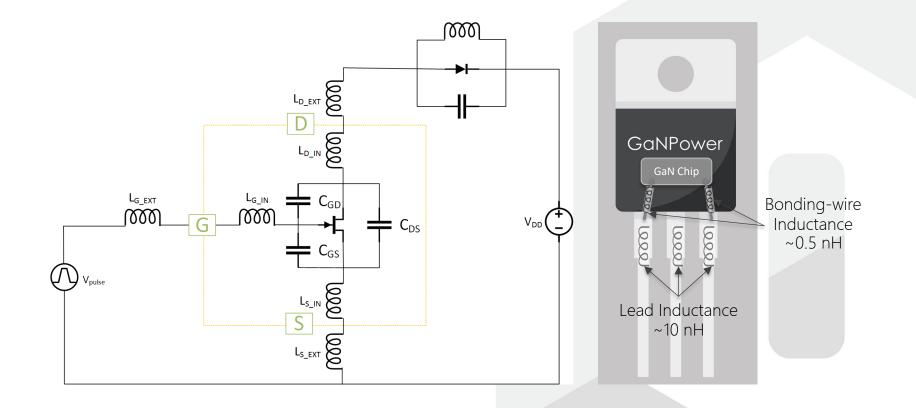

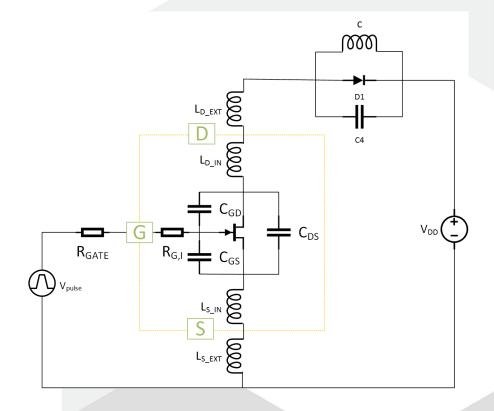

#### Gate Driving: Parasitic Inductance

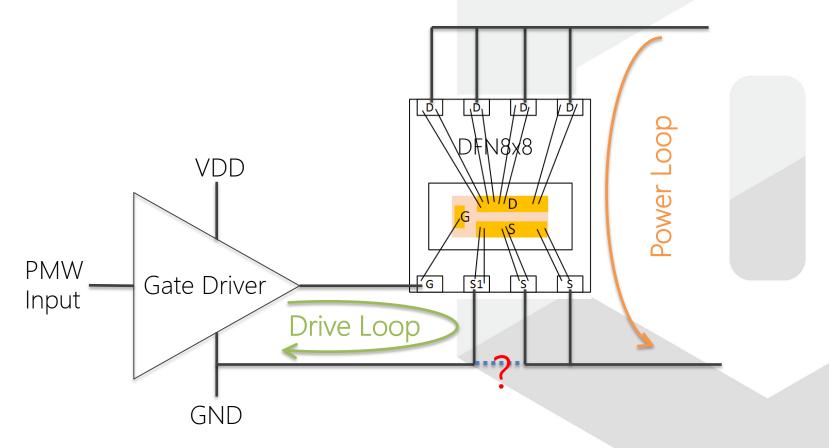

## Gate Driving: Kelvin Source

Some device packaging types, such as DFN, have kelvin source pins, properly connecting the kelvin source to the drive loop will minimize the common source inductance (CSI)

$\succ$

. . . .

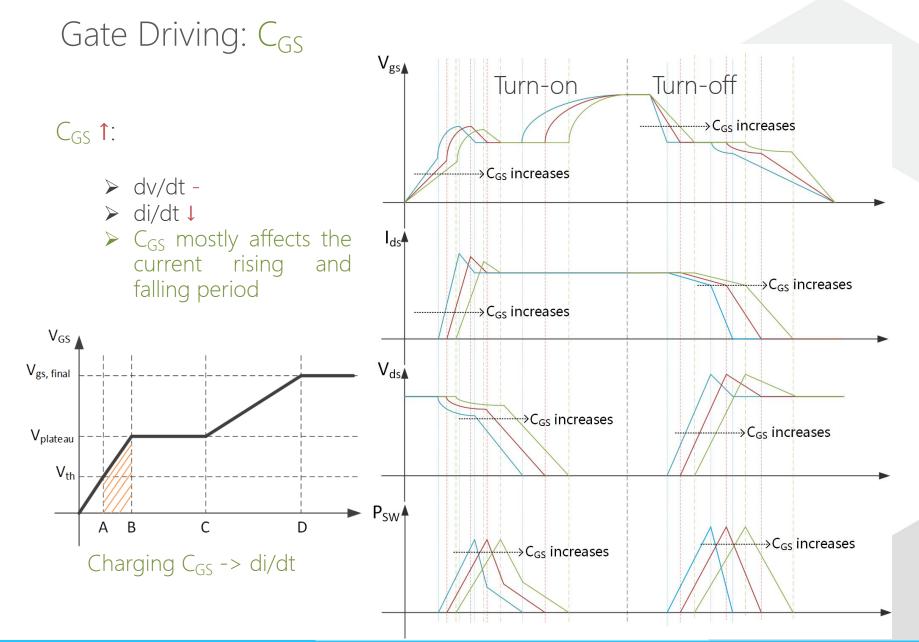

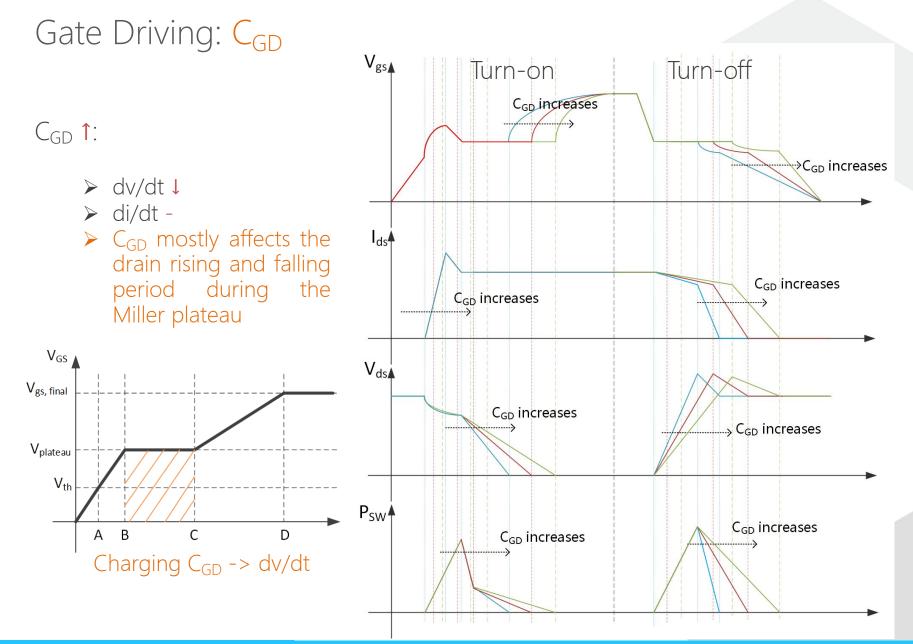

#### Gate Driving: Parameters that affect switching loss

- ➢ Gate resistance R<sub>g</sub>

- ➢ Gate to source capacitance C<sub>GS</sub>

- ► Gate to drain capacitance C<sub>GD</sub>

- ➢ Drain to source capacitance C<sub>DS</sub>

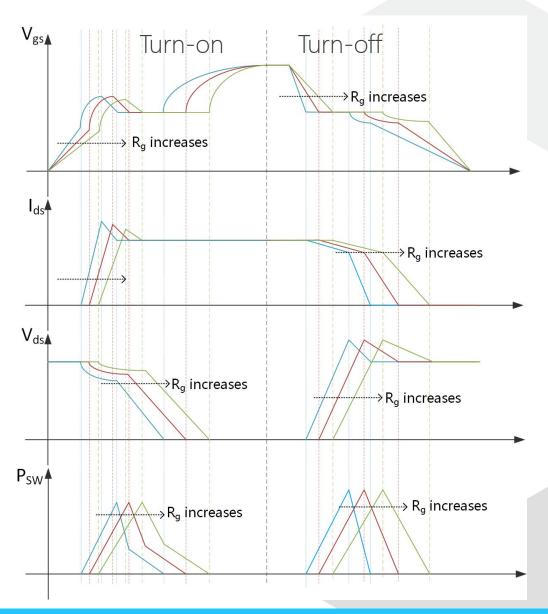

## Gate Driving: R<sub>g</sub>

R<sub>g</sub>↑:

- ≻ dv/dt↓

- ≻ di/dt↓

- ➢ Reduces switching speed

- Increase switching loss

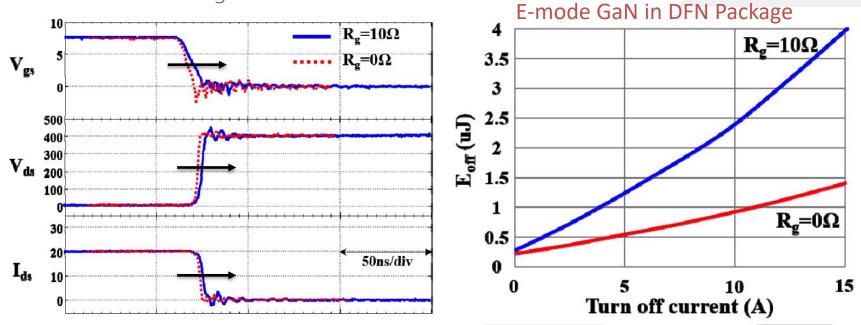

Gate Driving: R<sub>q</sub> (Experimental)

- $\checkmark$  R<sub>q</sub> limits the gate charging and discharging current and reduces dv/dt and di/dt slew rate

- ✓ Larger R<sub>g</sub> will increase switching loss, especially for turn-off

- $\checkmark$  A properly selected R<sub>q</sub> can mitigate the EMI issue that stems from high switching speed

Source: X. Huang, T. Liu, B. Li, F. C. Lee, and Q. Li, "Evaluation and applications of 600V/650V enhancement-mode GaN devices," 2015 WiPDA

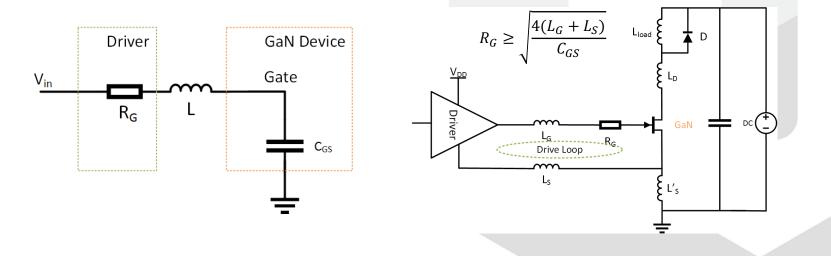

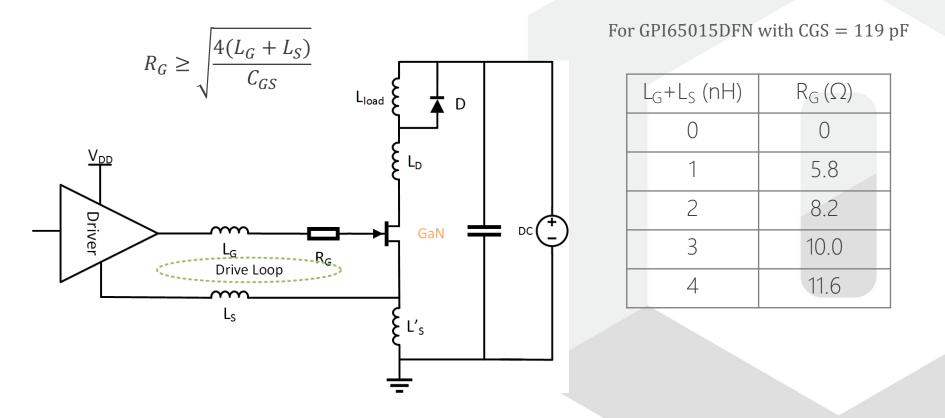

#### Gate Driving : R<sub>g</sub> Design Considerations

Trade off between fast switching and ringing

- > Equivalent RLC circuit for voltage driven topology:

- > Small  $R_G \downarrow \Rightarrow$  fast switching  $\uparrow \Rightarrow$  large ringing  $\uparrow$

- $\succ$  Large R<sub>G</sub> ↑ ⇒ slow switching ↓ ⇒ small ringing ↓

- Ringing causes Conducted Electromagnetic Interference (CEMI)

http://www.electronicdesign.com/power/take-practical-path-toward-high-performance-power-conversion

#### Gate Driving : R<sub>g</sub> Design Considerations

> To avoid ringing, with certain  $L_G$ ,  $L_S$  and  $C_{GS}$ ,  $R_G$  can be calculated as:

http://www.electronicdesign.com/power/take-practical-path-toward-high-performance-power-conversion

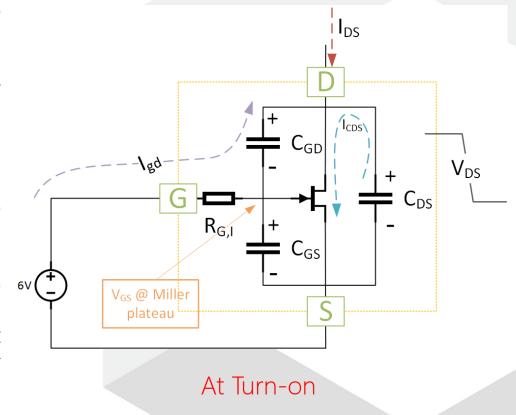

#### Gate Driving: Adding External C<sub>DS</sub>

- Adding external C<sub>DS</sub> capacitance does not reduce dv/dt at turn-on

- When the device turns on, at Miller plateau, drain voltage drops from V<sub>D</sub> to 0

- dv/dt is governed by the C<sub>gd</sub> and discharging current I<sub>gd</sub> from the gate driver

- Paralleling external capacitance to C<sub>ds</sub> doesn't impact dv/dt at turn-on, but it will add extra channel current I<sub>CDS</sub> that increases switching loss for hard-switching

#### Gate Driving : Adding External C<sub>DS</sub>

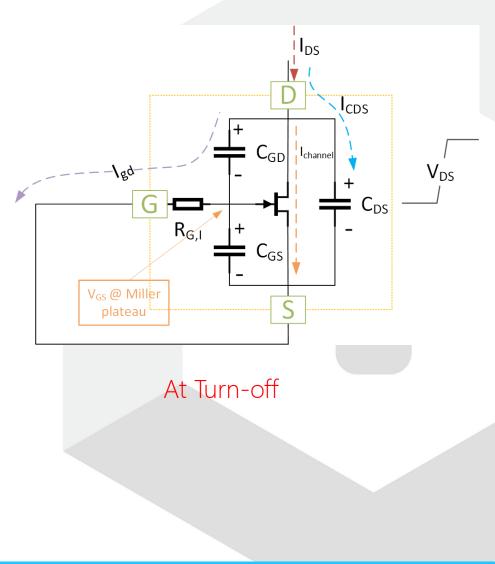

- ➢ When the device turns off, at Miller plateau, drain voltage rises from 0 to V<sub>D</sub>

- >  $I_{DS}$  from the drain is diverted into three parts:  $I_{gd}$  for charging  $C_{GD}$ ,  $I_{CDS}$  for charging  $C_{DS}$  and the rest goes through the channel ( $I_{channel}$ )

- dv/dt at turning-off is governed by C<sub>GD</sub> and C<sub>DS</sub>. Increasing C<sub>DS</sub> will reduce dv/dt, especially if I<sub>channel</sub> is relatively small

- I<sub>CDS</sub> will divert the current in the channel and reduces switching loss at turn-off (but increases turning-on loss at the same time for hard switching)

- If paralleling C<sub>DS</sub> is required to improve EMI, the value should be large enough so that the dv/dt rate at turn-off can be modulated

## Contents

#### ➢ Session 1: GaN devices basics

#### ➢ Session 2: Gate Driving

- ➢ Gate driving basics

- High dv/dt and di/dt issues

- ➢ Gate drivers and isolation

- Gate drive related power loss calculations

- ➢ Co-package and monolithic GaN IC

➢ Session 3: GaN Applications

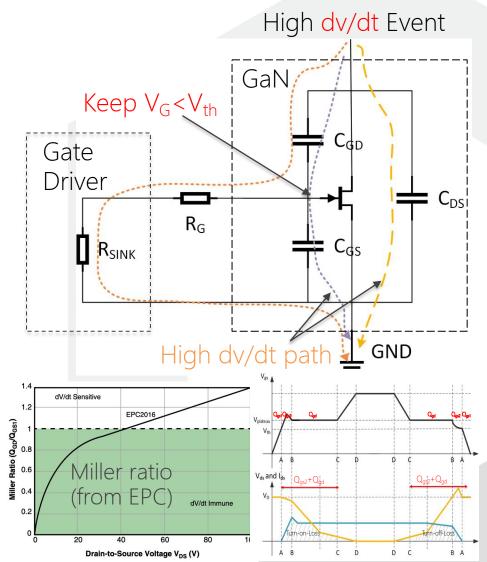

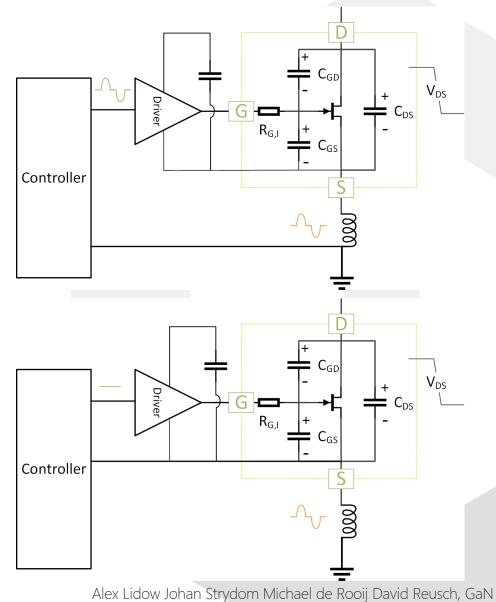

- High dv/dt charges parasitic capacitances. C<sub>DS</sub> is charged during this period, as well as the series connected C<sub>GD</sub> and C<sub>GS</sub>

- ➤ If the V<sub>GS</sub> gets higher than V<sub>th</sub> due to C<sub>GS</sub> charging, the device unintentionally switches on, which will lower overall efficiency. This is called Miller turn-on

- A by-pass can divert the current that flows through Miller capacitance to avoid false turnon

- Miller ratio (Q<sub>GD</sub>/Q<sub>GS1</sub>) can be used to determine how fragile the devices are due to Miller false turn-on. If the ratio smaller than 1, the device is guaranteed no false turn-on, However, many commercial devices cannot keep the ratio below 1

- Miller ratio also depends on applied V<sub>ds</sub>, since Q<sub>gd</sub> is a function of V<sub>ds</sub>. Higher V<sub>ds</sub> yields larger Q<sub>gd</sub> and thus more sensitive to dv/dt

Alex Lidow Johan Strydom Michael de Rooij David Reusch, GaN TRANSISTORS FOR EFFICIENT POWER CONVERSION, Wiley

## GaN Device dv/dt issue: no pull-down path

With no pull-down current from external driver :

$$V_{GS} = V_{DS} \frac{C_{GD}}{C_{GS} + C_{GD}}$$

In order to maintain  $V_{GS} < V_{TH}$  so that GaN device won't suffer from false turn-on, the maximum  $V_{DS}$  can be calculated as :

$$V_{DS,max} \le V_{TH} \frac{C_{GS} + C_{GD}}{C_{GD}}$$

The calculated  $V_{\text{DS},\text{max}}$  value can be quite small

Texas Instruments: Estimating MOSFET Parameters from the Data Sheet

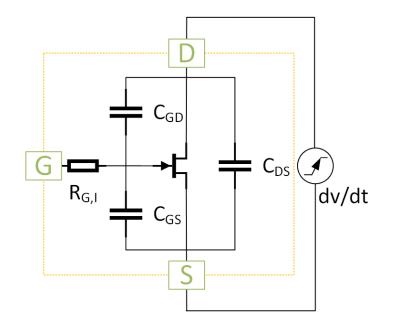

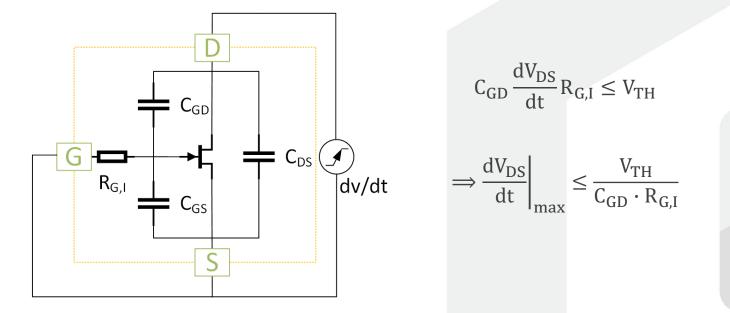

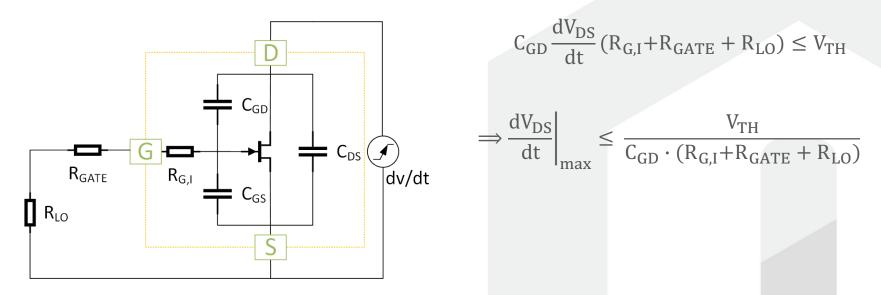

### GaN device dv/dt Issue: The intrinsic dv/dt limit

If the external driver resistance is 0, which means G and S are shorted, this is to calculate the intrinsic dv/dt limit

For example :  $C_{GD} = C_{rss} = 4 \text{ pF} (@VDS = 400V)$ ;  $C_{GS} = C_{iss} - C_{rss} = 123 - 4 = 119 \text{ pF} (@VDS = 400V)$ ;  $R_{G,I} = 1.5\Omega$

$$\frac{\mathrm{dV}_{\mathrm{DS}}}{\mathrm{dt}}\Big|_{\mathrm{max}} \le \frac{\mathrm{V}_{\mathrm{TH}}}{\mathrm{C}_{\mathrm{GD}} \cdot \mathrm{R}_{\mathrm{G,I}}} = \frac{1.41\mathrm{V}}{4\mathrm{pF} \times 1.5\Omega} = 235\mathrm{V/ns}$$

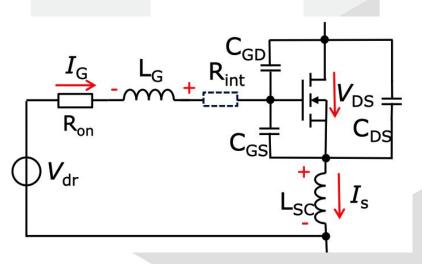

## GaN device dv/dt issue: A practical design

In a practical design, with external gate resistance R<sub>GATE</sub> and driver resistance R<sub>LO</sub>

For example :  $C_{GD} = C_{rss} = 4 \text{ pF}$ ;  $C_{GS} = C_{iss} - C_{rss} = 123 - 4 = 119 \text{ pF}$ ;  $R_{G,I} = 1.5 \Omega$ ; with gate driver from TI UCC27611:  $R_{LO} = 0.35 \Omega$ ; and assume  $R_{GATE} = 0.5 \Omega$  and  $@V_{DS}=400V$

$$\Rightarrow \frac{\mathrm{dV}_{\mathrm{DS}}}{\mathrm{dt}}\Big|_{\mathrm{max}} \le \frac{\mathrm{V}_{\mathrm{TH}}}{\mathrm{C}_{\mathrm{GD}} \cdot (\mathrm{R}_{\mathrm{G,I}} + \mathrm{R}_{\mathrm{GATE}} + \mathrm{R}_{\mathrm{LO}})} = \frac{1.41\mathrm{V}}{4 \,\mathrm{pF} \cdot (1.5\Omega + 0.35 \,\Omega + 0.5 \,\Omega)} = 150\mathrm{V/ns}$$

Low impedance turn-off drive-loop is critical for designs with GaN due to high dv/dt, especially for 650V devices

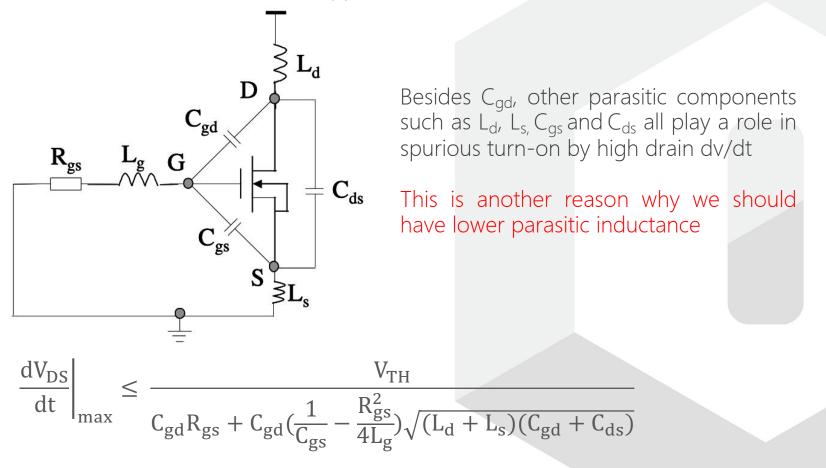

## GaN device dv/dt issue: A more comprehensive approach

A more comprehensive analysis was done by a group of researchers at Virginia Tech for MOSFET before, and it can be applied to GaN as well

Yuming Bai, Deva Pattanayak\*, Alex Q. Huang, Analysis of dv/dt Induced Spurious Turn-on of MOSFET, Virginia Tech

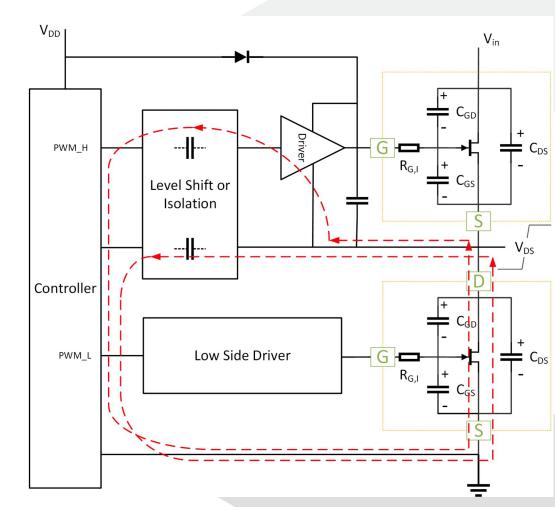

## GaN dv/dt issues: High Side

- With high positive and negative dv/dt slew rate of GaN, the common mode current can flow through the level-shifter or isolator of the high side switch

- It can cause ground bounce within the level shifter and even change logic states

- A smaller parasitic capacitance from the level-shifter or isolator is desirable, which will give a higher CMTI (common mode transient immunity)

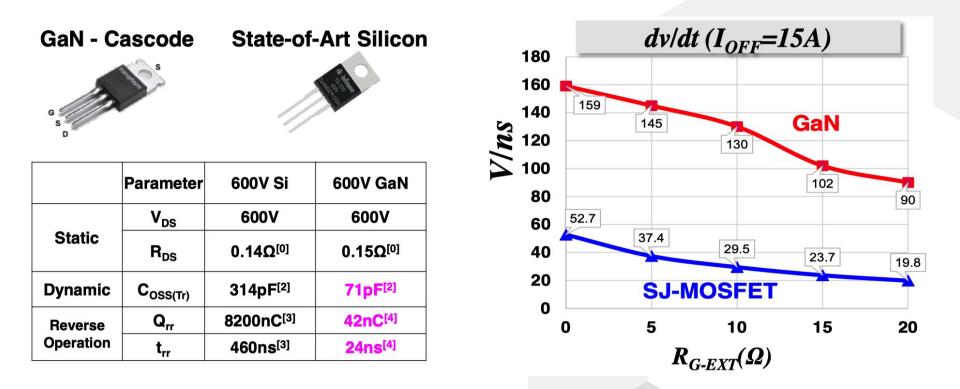

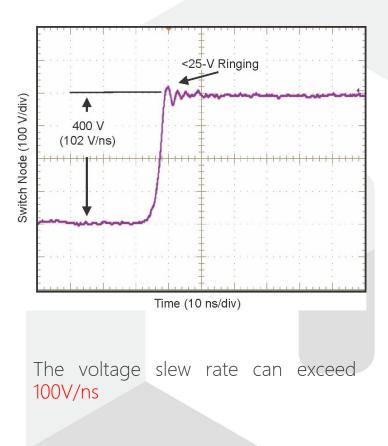

#### GaN vs. SJ MOS in terms of dv/dt

GaN has much higher dv/dt and di/dt than SJ MOS, special designs are necessary and drivers with high CMTI (Common mode transient immunity) is necessary

Wei Zhang, A Deep Dive of Isolated Gate Driver Robustness – dv/dt (CMTI) and di/dt, TI, APEC 2018

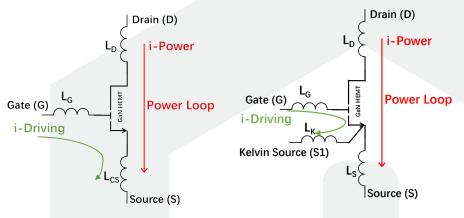

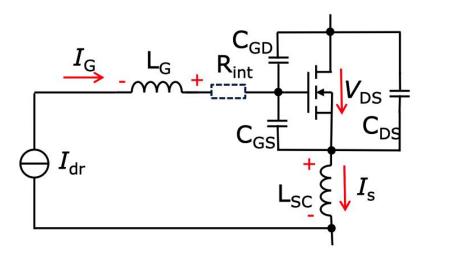

#### Common Source Inductance (CSI) and di/dt issues

- The common source inductance (CSI) is shared by the power loop and the drive loop

- Voltage across the CSI will be induced by the high current slew rate di/dt during switching period

- During device turn-on, this voltage counteracts with the voltage on the gate and elongates the turn-on time

- During device turn-off, this voltage increases the gate voltage, delays the turn-off time and causes ringing and false turn-on

- This negative feedback brings longer voltage-current overlap and increases switching loss

- A Kelvin pin is generally required to separate power and driving loop

Without Kelvin Source

With Kelvin Source

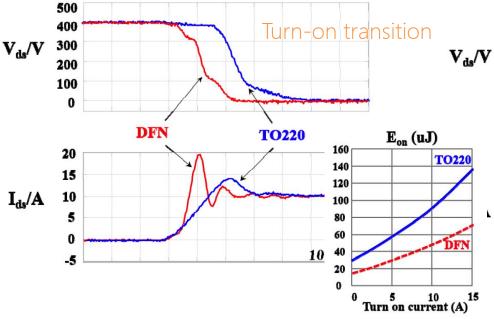

| Туре  | L <sub>G</sub> (nH) | L <sub>s</sub> (nH) | L <sub>D</sub> (nH) |

|-------|---------------------|---------------------|---------------------|

| TO220 | 3.6                 | 3.9                 | 2.3                 |

| DFN   | 2.4                 | 0.9                 | 1.3                 |

Xiucheng Huang, Tao Liu, Bin Li, Fred C. Lee, and Qiang Li Evaluation and Applications of 600V/650V Enhancement-Mode GaN Devices , 2015 WiPDA

## Ground Bounce

- If controller ground is tied to the power ground, the controller logic might be affected by the voltage pulses on the CSI (created by large high voltage slew rates across capacitors that generates large current pulses of short duration), which is called "ground bounce"

- Ground bounce can alter the normal device switching and lead to unwanted device behaviors

- One way to mitigate this issue is to tie the controller ground to the driver ground

TRANSISTORS FOR EFFICIENT POWER CONVERSION, Wiley

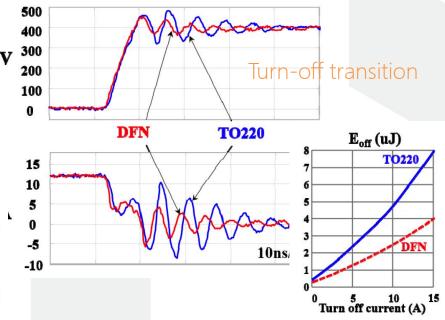

DFN vs. TO220 GaN in Hard-Switching (CSI Issue)

CSI affects di/dt, not dv/dt

- For turn-on, a lower di/dt can be observed for TO220 with CSI and no kelvin pin (due to I<sub>q</sub>I)

- Voltage transition is postponed due to increased current transition time

- ➢ Higher E₀n loss for TO220

- For turn-off, there is no voltage transition delay, since voltage rises before current falls

- di/dt rate is not much different, since most of the current transition we observed are for C<sub>oss</sub> charging

- However, a severe ringing occurred in TO220 that may indicate a false turn-on. E<sub>off</sub> loss is higher for TO220

Xiucheng Huang, Tao Liu, Bin Li, Fred C. Lee, and Qiang Li; Evaluation and Applications of 600V/650V Enhancement-Mode GaN Devices, 2015 WiPDA

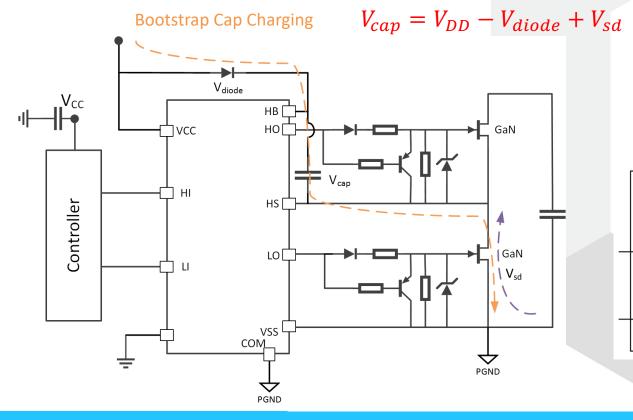

#### Gate Driving: Bootstrap

- ➢ If a bi-polar gate voltage (negative for turning-off) is applied, V<sub>sd</sub> for GaN devices can be quite large (several Volt)

- Bootstrap capacitor can be over-charged to cause damage to upper GaN switch

VDD

UVLO & Clamp

UVLC

DBoot

Level Shift

## Contents

#### ➢ Session 1: GaN devices basics

#### ➢ Session 2: GaN Gate Driving

- ➢ Gate driving basics

- ➢ High dv/dt and di/dt issues

- Gate drivers and isolation

- Gate drive related power loss calculations

- Co-package and monolithic GaN IC

➢ Session 3: GaN Applications

## Gate Voltage Requirements

| V <sub>ds</sub> Ratings | 20~650V | ≥650V    | ≥650V    | ≤1200V    |

|-------------------------|---------|----------|----------|-----------|

| Optimal V <sub>gs</sub> | 0~+15V  | -10~+15V | -5~+20V  | -5~+6V    |

| Max V <sub>gs</sub>     | ±20V    | ±20V     | -10~+25V | -10 ~ +7V |

#### Commercial Discrete 650V E-Mode GaN Driver Examples

| GaN Drivers | Vendor                 | Configur<br>ation | Sink /<br>Source | VDD Supply<br>Voltage | Gate Drive Voltage | Pull-up / Pull-<br>down<br>Resistance | Propagation<br>Delay |

|-------------|------------------------|-------------------|------------------|-----------------------|--------------------|---------------------------------------|----------------------|

| LM5114      | TI                     | Single-<br>Sided  | 7.6A /<br>1.3A   | 4~12.6V               | ~VDD               | 2Ω /0.23Ω                             | 12ns                 |

| UCC27611    | TI                     | Single-<br>Sided  | 4A /6A           | 4~18V                 | 5V                 | 1Ω /0.35Ω                             | 14ns                 |

| UCC27517    | TI                     | Single-<br>Sided  | 4A/4A            | 4.5~18V               | ~VDD               | 5Ω /0.5Ω                              | 13ns                 |

| MAX5048C    | Maxim<br>Integrated    | Single-<br>Sided  | 7A /3A           | 4~14V                 | ~VDD               | 0.84Ω /0.3Ω                           | 8ns                  |

| FAN3122     | Fairchild /<br>ON-Semi | Single-<br>Sided  | 9.7A<br>/7.1A    | 4.5V to 18V           | ~VDD               | NA                                    | 20ns                 |

| Si8271      | Silicon Lab            | Single-<br>Sided  | 4A /4A           | 4.2V to 30V           | ~VDD               | 2.7Ω /1Ω                              | 60ns (max)           |

| Si8273      | Silicon Lab            | Half-<br>bridge   | 4A /4A           | 4.2V to 30V           | ~VDD               | 2.7Ω /1Ω                              | 60ns (max)           |

| NCP51820    | ON                     | Half-<br>Bridge   | 2A/1A            | 9V to 17V             | 5.5V               | N/A                                   | 25ns                 |

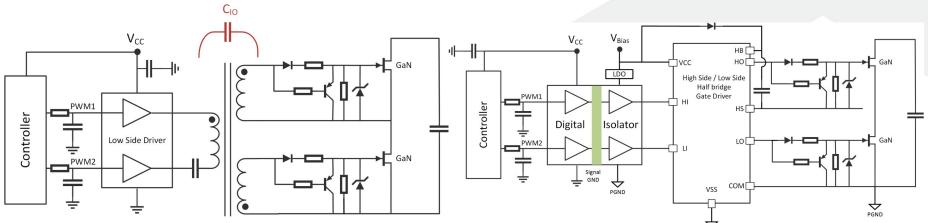

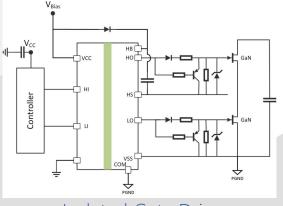

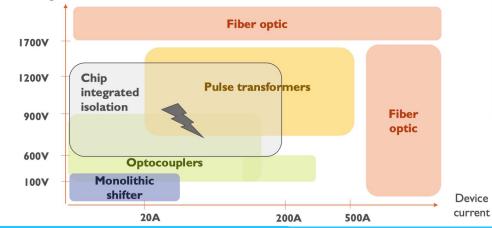

## Isolated Gate Driving

In order to meet IEC 61010 isolation requirement, three types of isolated gate driving are available:

Gate Isolation with Transformer

|                 | Transformer Iso       | Digital Isolator | Isolated driver |

|-----------------|-----------------------|------------------|-----------------|

| Prop. Delay     | 20 ns                 | 100 ns           | 19 ns (Typical) |

| Bias Power      | No                    | Yes              | Yes             |

| C <sub>IO</sub> | ≥10 pF                | <1 pF            | <1 pF           |

| Parasitics      | Large L <sub>lk</sub> | Very Small       | Very Small      |

| Overshoot       | Large                 | Small            | Small           |

| Size            | Bulky                 | Small            | Very Small      |

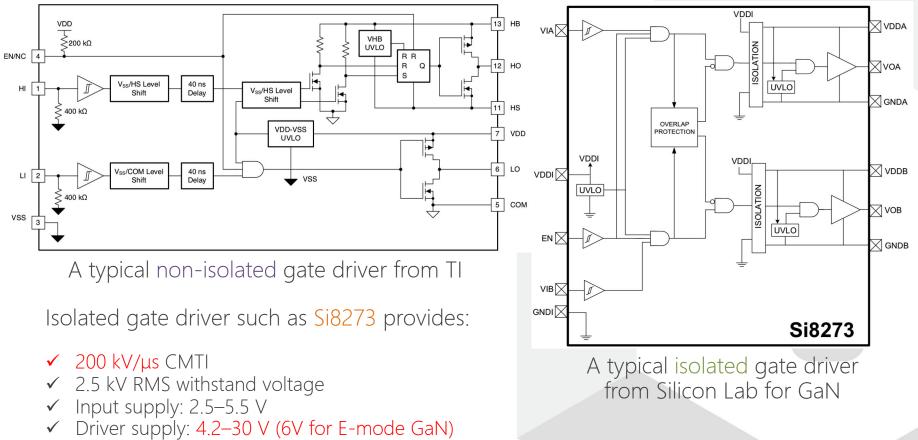

#### Isolated Gate Driver

Source: Wei Zhang, Mastering the art and fundamentals of high voltage gate driver; TI High Volt Interactive

Half Bridge Gate Driver : Isolated and Non-Isolated

✓ Prop. Delay: 60 ns (max)

UCC27714High-Speed, 600-VHigh-SideLow-SideGateDriver with 4-A Peak Output https://www.silabs.com/documents/public/data-sheets/Si827x.pdf

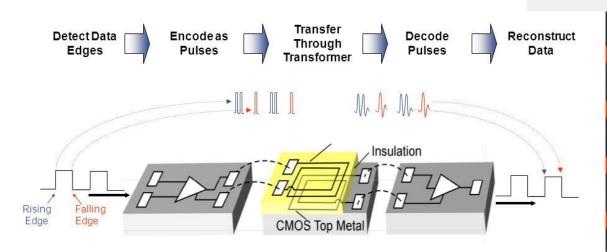

## Digital Isolation Technology: Magnetic Isolator

Magnetic isolator is based on chip-scale transformers, compared to optocoupler, magnetic couplers use low-stress, thick-film polyimide insulation to achieve thousands of volts of isolation that can be monolithically integrated with standard silicon ICs and can be fabricated in single-channel, multi-channel, and bidirectional configurations

- ✓ 4x improvement in data rate and timing specifications

- ✓ Integrates multiple isolation channels with other functions to reduce size and cost

- Operates at power levels up to 90% lower than optocouplers

- Minimizes external components needed to connect to other digital devices

- Increases reliability by eliminating LEDs used in optocouplers

Ref: Analog Devices: Standard Digital Isolators

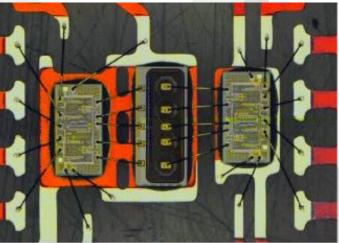

## Digital Isolation Technology: Capacitive Isolator

Capacitive isolation is made by adding capacitive isolation barrier on top of each die to connect in series, digital circuits are used for encoding and decoding various signals through the isolation barrier. A capacitive isolator's inability to pass DC signals makes it inherently the right choice for isolation

1, Capacitive Isolation: The Future AC/DC Power Conversion, Monolithic Power Systems 2, https://www.silabs.com/documents/public/data-sheets/Si827x.pdf 3, TI: Digital Isolators

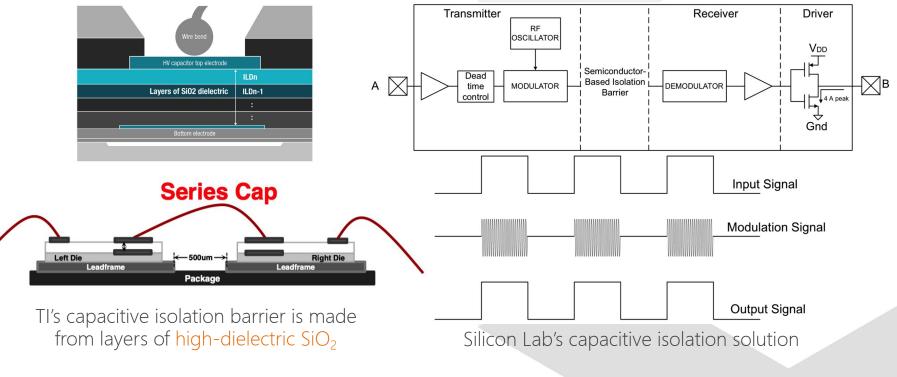

#### Isolation Technology: Comparison

|                             | Isolation          | dv/dt<br>immunity | Propagation<br>delay | Integration level                              | Independent<br>power supply<br>needed at the<br>secondary | Reliability<br>(over time &<br>harsh<br>environment) | Cost     |

|-----------------------------|--------------------|-------------------|----------------------|------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|----------|

| Optocouplers                | Few kV             | >50kV/µs          | >400ns               | Medium                                         | Yes                                                       | Aging issues                                         | \$       |

| Fiber optic                 | Several 10's<br>kV | >100kV′s/µs       | Negligible           | Medium                                         | Yes                                                       | Good<br>reliability                                  | \$\$\$\$ |

| Monolithic<br>level shifter | None               | 50kV/µs           | -                    | Integrated on<br>the IC                        | No                                                        | -                                                    | \$       |

| Pulse<br>transformer        | Several kV         | >50kV/µs          | <100 ns              | Bulky                                          | No                                                        | Reliable                                             | \$       |

| Digital<br>isolation        | Several kV         | >100kV/µs         | ~20 ns               | Integrated on-<br>chip or driver IC<br>package | Yes                                                       | Very reliable                                        | \$\$     |

Device voltage

Gate Drivers market evolution: coreless isolation and WBG specific solutions, Yole Development, APEC 2018

© Fred Yue Fu (傅玥), GaNPower International Inc.

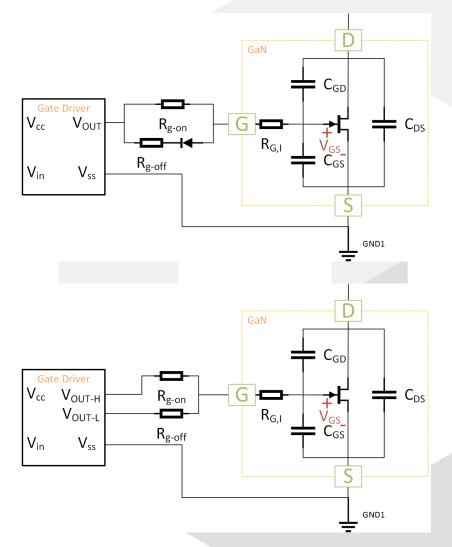

# Choosing GaN Gate Driver and R<sub>g</sub>

- If possible, gate drivers with individual turn-on and turn-off pins are recommended

- Use separate drive loops for turn-on and turn-off. Turn-off loop low impedance is recommended to avoid false turn-on and oscillations

- Proper selection of R<sub>g-on</sub> vs. R<sub>g-off</sub> is critical. Normally the ratio of R<sub>g-on</sub> to R<sub>g-off</sub> can be chosen between 5 to 10

\*Source: GN001 Application Guide: Design with GaN Enhancement mode HEMT, GaN Systems

#### Current-source and Voltage-source Gate Drivers

| Current-source gate driver                                                                                  | Voltage-source gate driver                                                                                       |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Current sources have a high resistive output<br>by default                                                  | Voltage sources shall be as low resistive as possible                                                            |

| Any additional voltage drop in the gate drive loop has no influence on the gate current $I_g$ inside limits | Any additional voltage drop in the gate drive loop has immediate influence on the gate current ${\sf I}_{\sf g}$ |

| Supposed to damp oscillations                                                                               | Prone to oscillations                                                                                            |

Ref: Turn-on performance comparison of current-source vs. voltage-source gate drivers, Infineon, APEC 2018

# Contents

#### ➢ Session 1: GaN devices basics

#### ➢ Session 2: GaN Gate Driving

- ➢ Gate driving basics

- ➢ High dv/dt and di/dt issues

- ➢ Gate drivers and isolation

- Gate drive related power loss calculations

- Co-package and monolithic GaN IC

➢ Session 3: GaN Applications

#### GaN Device Power Loss Analysis

- Conduction Loss: P<sub>Cond</sub>=I<sub>D</sub><sup>2</sup> · R<sub>dson</sub> · D (D: Duty Cycle)

- Switching Loss: P<sub>Switching</sub>=1/2 · I<sub>D</sub> · V<sub>D</sub> · (t<sub>on</sub>+t<sub>off</sub>) · f<sub>sw</sub>

- Gate Driving Loss: P<sub>Driving</sub>=V<sub>g</sub> · Q<sub>g</sub> · f<sub>sw</sub>

- Power Loss from C<sub>oss</sub> P<sub>COSS</sub>=E<sub>OSS</sub> · f<sub>sw</sub>

# GaN Power Loss Chart

Conduction Loss Switching Loss Gate Driving Loss

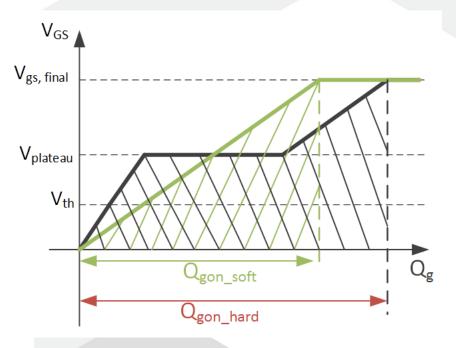

#### GaN Gate Driving Loss

With same gate driver, soft-switching such as ZVS has a lower turn-on gate driving loss than hard-switching:

$$P_{gate\_dr\_on} = E_{on\_soft} \cdot f_{sw} = V_{gs} \cdot Q_{gon\_soft} \cdot f_{sw}$$

$$P_{gate\_dr\_on} = E_{on\_hard} \cdot f_{sw} = V_{gs} \cdot Q_{gon\_hard} \cdot f_{sw}$$

Wei Zhang, Mastering the art and fundamentals of high voltage gate driver; TI High Volt Interactive

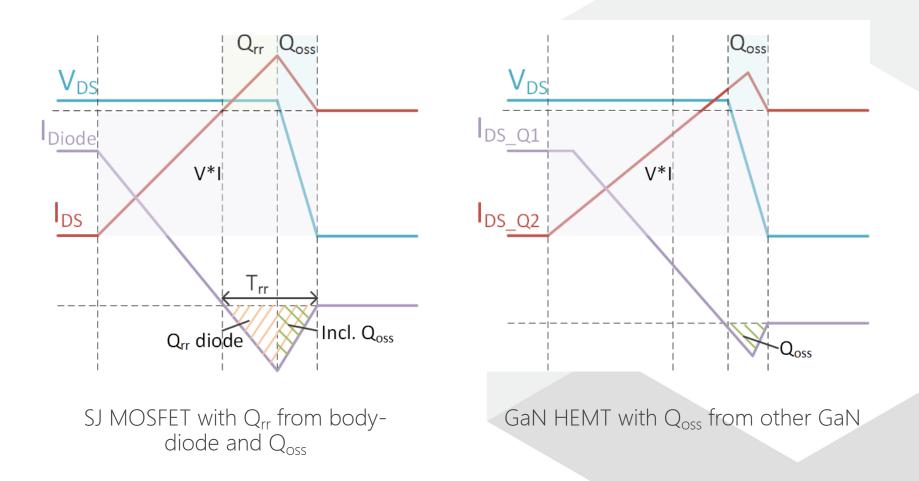

#### GaN vs. SJ MOS: Q<sub>rr</sub> and Q<sub>oss</sub> Loss

Peter Di Maso, Lucas Lu, GaN E-HEMTs Enable Innovation in Power Switching Applications, GaN Systems, APEC 2017

#### GaN Device Power Loss Analysis: Hard-Switching

$\succ$  With same R<sub>dson</sub> and same frequency, GaN power loss vs. Si:

$P_{hard\_SW} = P_{cond} + P_{sw} + P_{coss} + P_{gate} + P_{sd} + P_{rr}$

|                      | sj mos | GaN    | Remark                                          |

|----------------------|--------|--------|-------------------------------------------------|

| P <sub>cond</sub>    | same   | same   | Same R <sub>dson</sub>                          |

| P <sub>sw</sub>      | higher | lower  | Due to GaN has smaller $Q_{GS2}$ and $Q_{GD}$   |

| P <sub>coss</sub>    | higher | lower  | GaN has a lower C <sub>oss</sub>                |

| P <sub>gate</sub>    | higher | lower  | GaN has lower gate drive voltage                |

| P <sub>sd</sub>      | lower  | higher | GaN has a higher V <sub>sd</sub>                |

| P <sub>rr</sub>      | higher | none   | GaN has no Q <sub>rr</sub>                      |

| P <sub>hard_sw</sub> | higher | lower  | GaN has a lower total hard switching power loss |

# Contents

#### ➢ Session 1: GaN devices basics

#### ➢ Session 2: GaN Gate Driving

- ➢ Gate driving basics

- ➢ High dv/dt and di/dt issues

- ➢ Gate drivers and isolation

- Gate drive related power loss calculations

- > Co-package and monolithic GaN IC

➢ Session 3: GaN Applications

| PARAMETER<br>V <sub>DD</sub> (V <sub>DD</sub> operating voltage) |                                          | TEST CONDITION<br>(T <sub>J</sub> ) range of -40°C to 125°C |                      | MIN<br>MAX | TYP UNIT |

|------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------|----------------------|------------|----------|

|                                                                  |                                          |                                                             |                      | 5          | V        |

| UVLO                                                             | V <sub>DD</sub> under voltage<br>lockout | $V_{DD}$ Rising                                             | Tj=25℃               | 3.8        | V        |

| V <sub>DD</sub> undervoltage lo                                  |                                          | ckout hysteresis                                            |                      | 0.2        |          |

| I <sub>DD</sub> (V <sub>DD</sub> quiescent current)              |                                          | I <sub>N</sub> =I <sub>NB</sub> =0                          | T <sub>j</sub> =25°C | 0.01       | mA       |

| N-CHANN                                                          | EL OUTPUT                                |                                                             |                      |            | _        |

| R <sub>on-N</sub> (Driver output resistance-<br>pulling down)    |                                          | $V_{DD} = 5V, I_{N-OUT} = -100mA$                           |                      | 0.25       | Ω        |

| I <sub>PK-N</sub> (peak sink current)                            |                                          | C <sub>L</sub> = 10,000 pF                                  |                      | 5          | А        |

| P-CHANN                                                          | EL OUTPUT                                | •                                                           |                      | •          | •        |

| R <sub>on-P</sub> (Driver output resistance-<br>pulling up)      |                                          | $V_{DD} = 5 V, I_{N-OUT} = 50 mA$                           |                      | 2.1        | Ω        |

| I <sub>PK-P</sub> (peak source current)                          |                                          | C <sub>L</sub> = 10,000 pF                                  |                      | 1.3        | А        |

GPI65030CO: Si driver basic parameters

GPI65030CO: double-pulse test, rising edge of second pulse (turn-on @ second pulse). Yellow: Drain to Source Voltage; Blue: Drain to Source Current

| PARAMETER                               | TEST CONDITION (VDD=5V) |                                                 | MIN TYP<br>MAX | UNIT |

|-----------------------------------------|-------------------------|-------------------------------------------------|----------------|------|

| t <sub>R</sub> Rise time                | CL=1nf                  |                                                 | 5              | ns   |

| t <sub>F</sub> Fall time                | C <sub>L</sub> =1nf     |                                                 | 3              | ns   |

| t <sub>D-ON</sub> turn-on propagation   |                         | T <sub>j</sub> =25°C                            | 17             |      |

| delay                                   | C <sub>L</sub> =1nf     | (T <sub>J</sub> ) range<br>of -40°C to<br>125°C | 12.9<br>20     | ns   |

| t <sub>D-OFF</sub> turn-off propagation |                         | T <sub>j</sub> =25°C                            | 15.7           |      |

| delay                                   | CL=1nf                  | (T <sub>J</sub> ) range<br>of -40°C to<br>125°C | 13.5<br>18     | ns   |

GPI65030CO: Si driver dynamic parameters

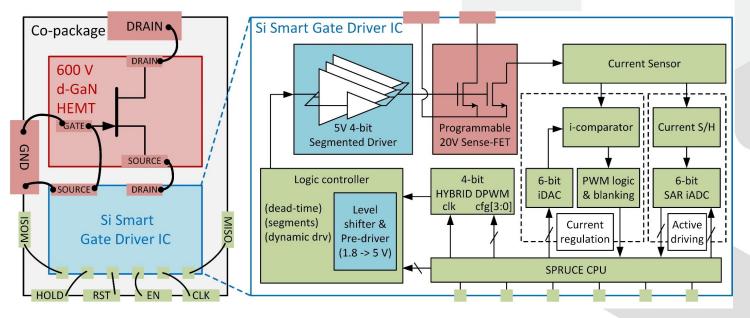

## Si Driver + GaN Co-package: D-Mode GaN

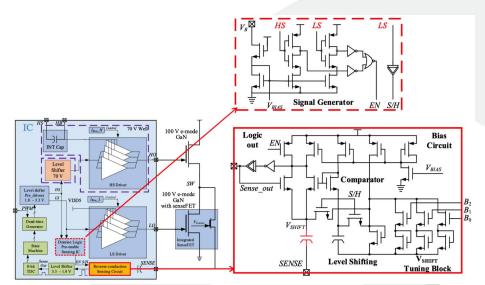

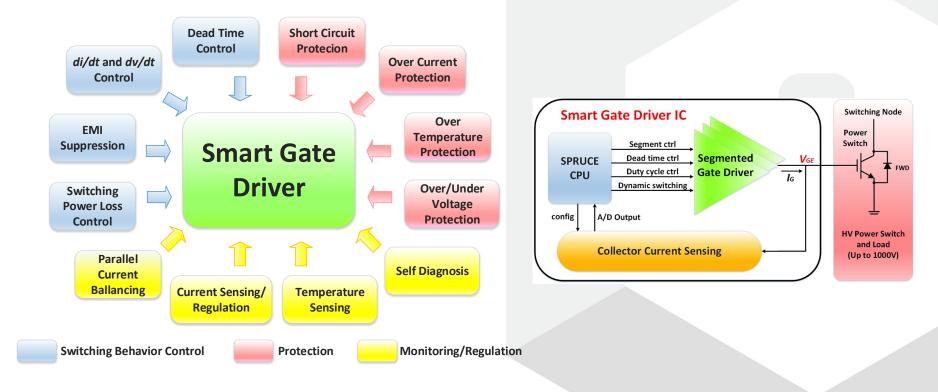

#### A smart gate driver IC for cascode D-GaN (By University of Toronto)

- Desired functions include

- $\checkmark$  Tunable output resistance

- ✓ Precise timing control

- $\checkmark$  Current sensing for regulation and protections purposes

- ✓ Dynamic driving techniques

- $\checkmark$  Change gate driving strength during switching

- ✓ Fully integrated controller circuits

- ✓ Flexible digital control

- ✓ Active driving ability under different load conditions

Jingshu Yu, Weijia Zhang, Andrew Shorten, Rophina Li and Wai Tung Ng, A Smart Gate Driver IC for GaN Power Transistors; ISPSD 2018

### Si Driver + GaN Co-package: D-Mode GaN

Jingshu Yu, Weijia Zhang, Andrew Shorten, Rophina Li and Wai Tung Ng, A Smart Gate Driver IC for GaN Power Transistors; ISPSD 2018

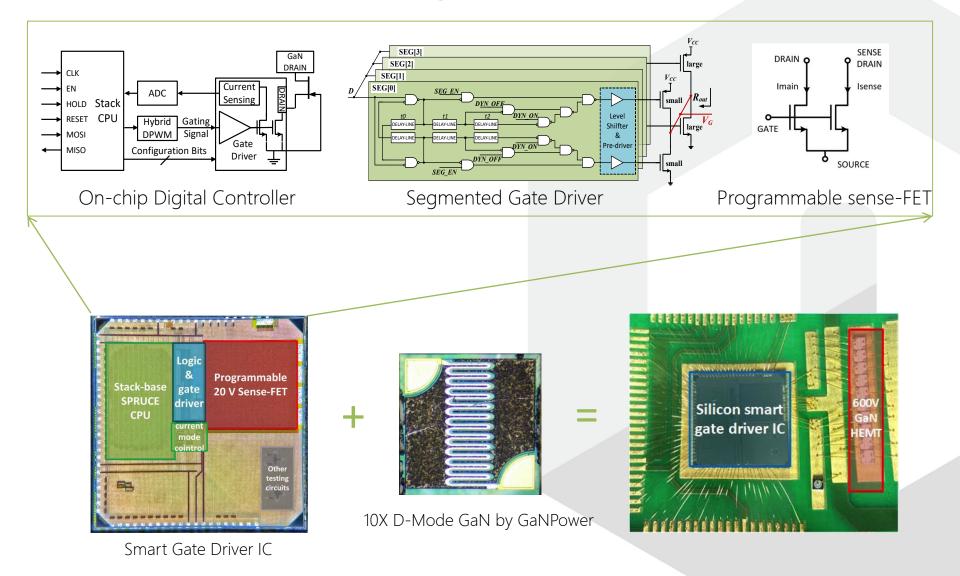

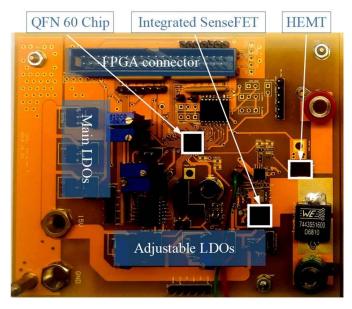

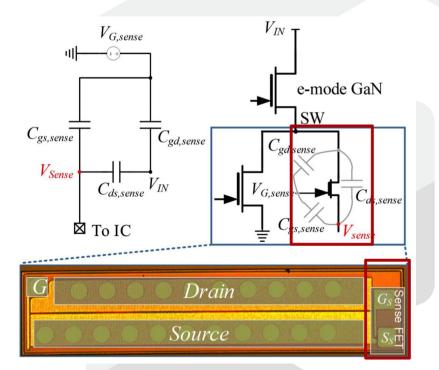

## Si Driver + GaN Co-package: E-GaN and SenseFET

A novel SenseFET by GaNPower helps researchers from University of Toronto won the prestigious 2019 IEEE ISPSD Charitat Young Researcher Award

Integrated GaN SenseFET

GaNPower SenseFET GaN, in collaboration with University of Toronto

Source: W.J. Zhang, Y.H. Leng, J.S. Yu, Y.S. Lu, C.Y. Cheng and W.T. Ng, A Gate Driver IC for Enhancement Mode GaN Power Transistors with Precise Dead-time Correction, ISPSD 2019

#### Si Driver + GaN Co-package: E-GaN and SenseFET

GP16501510 as HS and LS Provided by GaNPower

- > The SenseFET from GaNPower is rated at 100V/20m $\Omega$  with two extra leads for the sensing gate and sensing source

- > The current of the sensing source is designed to have a small match ratio while providing accurate sensing. However, the novelty is to use the SenseFET in a voltage clamping circuit to detect reverse conduction of the emode GaN low side output device while protecting the detection circuit from the high voltage swing at the switching node

- > The duration of this reverse conduction is then corrected by adjusting the dead-time in the following switching cycle to ensure optimum power conversion efficiency

- > The GaN SenseFET is conveniently packaged in an 8×8 8-lead DFN package

Source: W.J. Zhang, Y.H. Leng, J.S. Yu, Y.S. Lu, C.Y. Cheng and W.T. Ng, A Gate Driver IC for Enhancement Mode GaN Power Transistors with Precise Dead-time Correction, ISPSD 2019

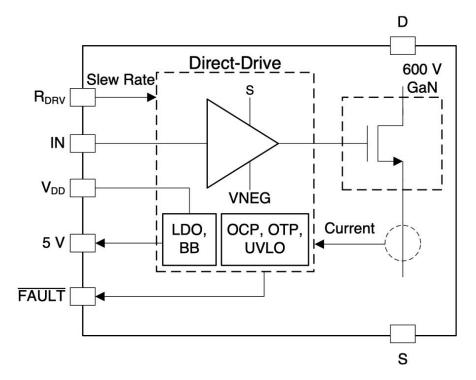

#### Si Driver + GaN Co-package: TI Direct-Drive

Direct-drive looks like a cascode method, in which a low voltage MOS is in series with high voltage D-mode GaN. The difference is that TI integrates the driver IC to drive the GaN directly, while the low voltage MOS is used to make the package normally-off

Source: LMG341xR070 600-V 70-m $\Omega$  GaN with Integrated Driver and Protection. TI datasheet

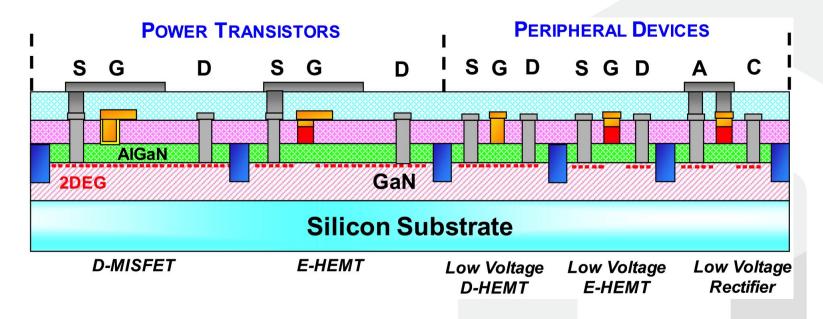

- Currently, mainstream GaN technology is using 6-inch wafer with 0.5um feature size

- ✓ This roughly equals to the silicon lateral BCD technology used 20 years ago

- ✓ GaN IC doesn't have P-type HEMT, due to ion-implantation of p-type materials such as Mg and subsequent thermal anneal very difficult to handle

- ✓ Instead, GaN IC is either using Direct-Coupled FET Logic (DCFL) with both E-mode and D-mode devices, or just use D-mode devices in the IC design

- ✓ Resistors, capacitors are available in GaN IC, much like 20 years ago in silicon BCD technology

| Gate Driver<br>for High side | High side Gate<br>Monitor | High side Transistor |

|------------------------------|---------------------------|----------------------|

|                              |                           |                      |

|                              |                           | DS DS                |

|                              |                           |                      |

| Gate Driver                  | Low side                  | Low side Transistor  |

| for Low side                 | Gate Monitor              | 1mm                  |

| Pana                         | asonic (                  | GaN IC               |

GaN-based Semiconductor Devices for Future Power Switching Systems; Hidetoshi Ishida, Ryo Kajitani, Yusuke Kinoshita, Hidekazu Umeda, Shinji Ujita, Masahiro Ogawa, Kenichiro Tanaka, Tatsuo Morita, Satoshi Tamura, Masahiro Ishida and Tetsuzo Ueda; IEDM 2016

Navitas APEC 2019 Industry paper

- ✓ Both active devices, such as high voltage and low voltage D-mode and E-mode HEMT are available

- ✓ Passive components, such as GaN-FET-based rectifiers, MIM capacitors and 2DEG resistors are available for analog functions

Source: Kevin J. Chen, Oliver Häberlen, Alex Lidow, Chun lin Tsai, Tetsuzo Ueda, Yasuhiro Uemoto and Yifeng Wu, GaN-on-Si Power Technology:, Devices and Applications IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 64, NO. 3, MARCH 2017

GaN IC, is it the future?

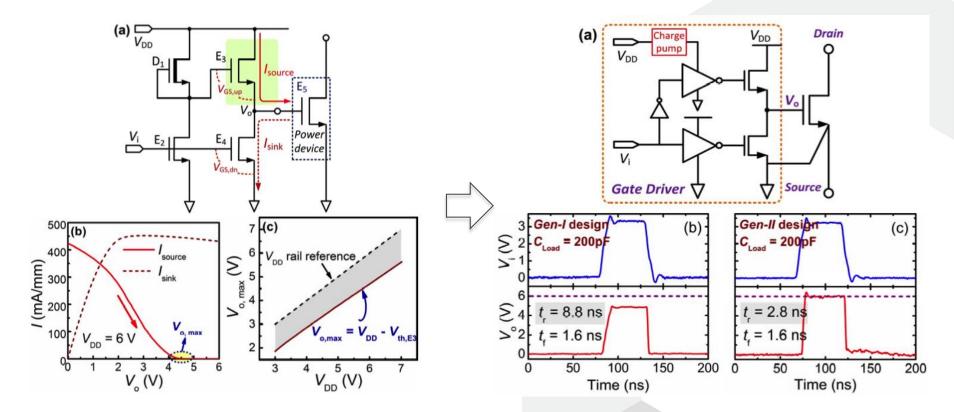

One of the first published monolithically integrated GaN IC design with two generations using directly-coupled FET Logic that combines both D-mode and Emode transistors

> Source: Gaofei Tang1, M.-H. Kwan2, Zhaofu Zhang1, Jiabei He1, Jiacheng Lei1, R.-Y. Su2, F.-W. Yao2, Y.-M. Lin2, J.-L. Yu2, Thomas Yang2, Chan-Hong Chern2, Tom Tsai2, H. C. Tuan2, Alexander Kalnitsky2, and Kevin J. Chen1, High-Speed, High-Reliability GaN Power Device with Integrated Gate Driver; Proceedings of the 30th International Symposium on Power Semiconductor Devices & ICs May 13-17, 2018, Chicago, USA

Numerous design has been reported for GaN IC, including simple logic functions such as NAND, NOR and comparators

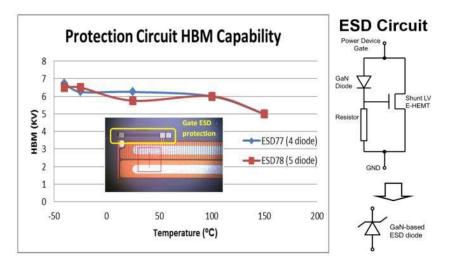

GaN integrated ESD protection circuit (<2% area) integrated to the gate of the power device on the GaN power device platform. Human body model ESD voltage on the gate can exceed 5 kV from -45 °C to 150 °C

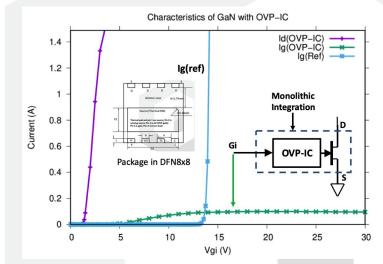

An over-voltage-protection (OVP) function offered by GaNPower provides gate voltage protection by clamping gate voltage below required maximum gate voltage of GaN when the driver output exceed the maximum

Source: Kevin J. Chen, Oliver Häberlen, Alex Lidow, Chun lin Tsai, Tetsuzo Ueda, Yasuhiro Uemoto and Yifeng Wu, GaN-on-Si Power Technology:, Devices and Applications IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 64, NO. 3, MARCH 2017

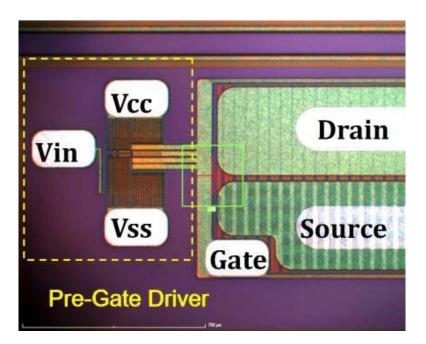

GaN integrated pre-gate driver (<5% area) integrated with a 120-mm E-mode GaN power device. Integration of devices shortens parasitic paths and thus achieves low ringing, short rise (8.5 ns) and fall (2.5 ns) time, and higher switching speed

Need more detailed analysis from the application side to fully compare the benefits and drawbacks of using either monolithically integrated GaN solution or Si driver + GaN solution

Source: Kevin J. Chen, Oliver Häberlen, Alex Lidow, Chun lin Tsai, Tetsuzo Ueda, Yasuhiro Uemoto and Yifeng Wu, GaN-on-Si Power Technology:, Devices and Applications IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 64, NO. 3, MARCH 2017

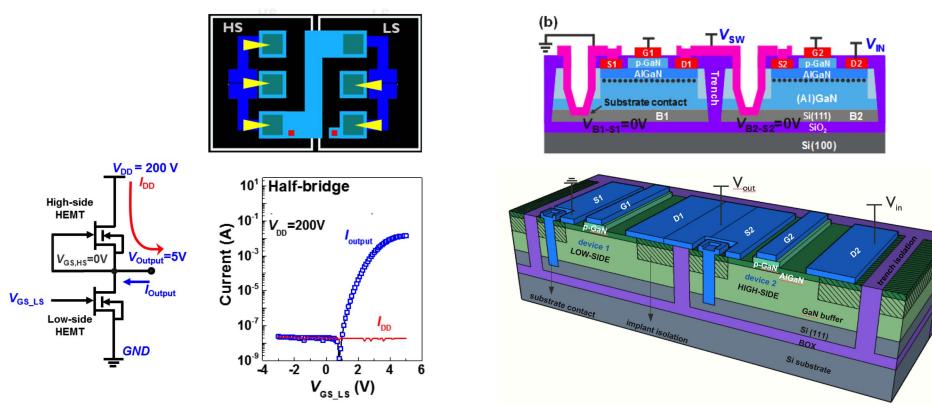

Perfect isolation between High Side and Low Side transistors in a GaN-based half-bridge on chip

Imec's GaN-IC approach

IMEC is offering GaN IC for MPW (multi-project-wafer) based on their GaN-on-SOI epitaxy. They have also demonstrated first high-side/low-side GaN-IC on chip with perfect isolation

Source: https://www.imec-int.com/en/200mm-GaN-on-Si-technology

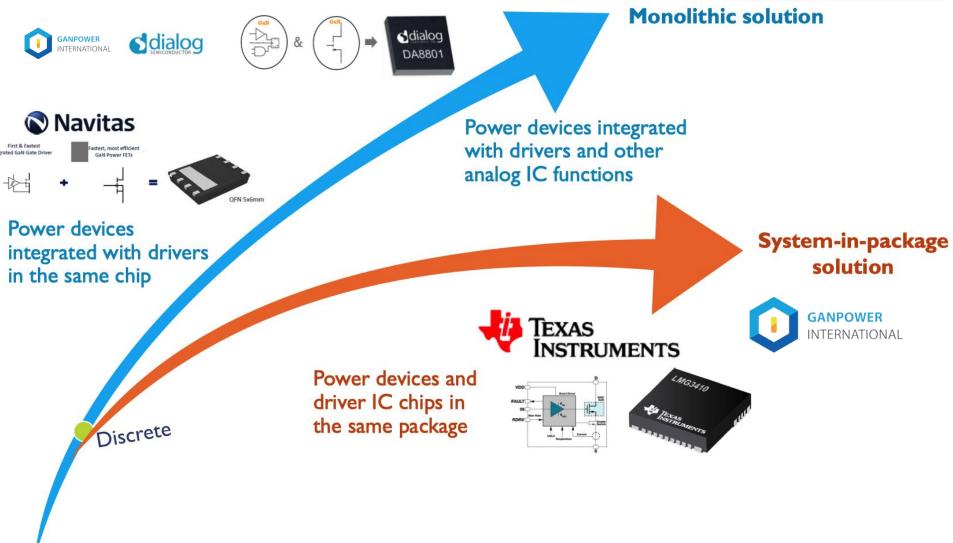

(From Yole Development with modifications). Gate Drivers market evolution: coreless isolation and WBG specific solutions, Yole Development, APEC 2018

While monolithic integration provides ultimate performance and eliminates on-board parasitics, silicon IC + GaN co-package can still provide more comprehensive functionalities -- at least for now

Ref: Design Trends in Smart Gate Driver ICs for Power MOSFETs and IGBTs, ASICON 2017

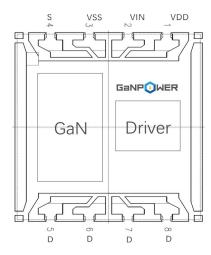

#### GaNPower Future Integrated Modules

## THANKS FOR WATCHING!

Contact us (Vancouver Headquarters) :

- (?) 230-3410 LOUGHEED HWY VANCOUVER, BC, V5M 2A4 CANADALGA

- 1.778.588.1119

- information@iganpower.com

#### 联系我们 (Greater China Region )

- 中国江苏省苏州市工业园区纳米技术国家大学科技园F0411

- +86-512-65267027

- sales@iganpower.com

Ultra High Frequency Power Conversion

WWW.IGANPOWER.COM 230-3410 LOUGHEED HWY VANCOUVER, BC, V5M 2A4 CANADA