# GaN Power HEMT Tutorial: GaN Basics

**GANPOWER INTERNATIONAL INC**

Fred Yue Fu (傅玥) Co-founder and COO GaNPower International Inc.

#### Contents

- > Session 1: GaN devices basics

- ➤ GaN, An Introduction

- > GaN Design, Fabrication and Testing

- ➤ GaN Compact Modeling and Reliability

- > Session 2: Gate Driving

- > Session 3: GaN Applications

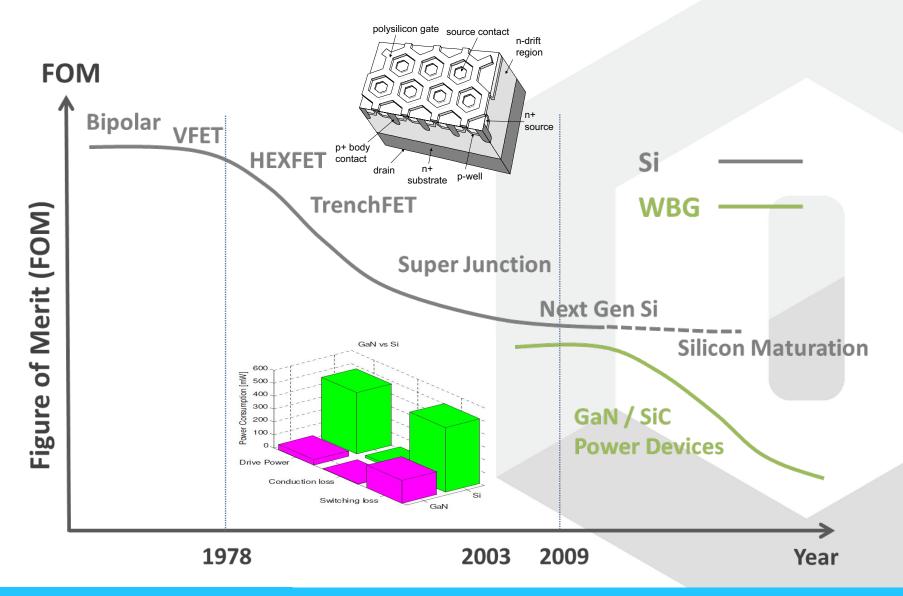

# Power Devices: History of Evolvements

| 1952                     | 1957                 | 1960s                       | 1970s                      | 1980s           | 2000                              | 2010              |

|--------------------------|----------------------|-----------------------------|----------------------------|-----------------|-----------------------------------|-------------------|

|                          |                      |                             |                            |                 |                                   | Ganpower          |

| Power Diode<br>Germanium | Thyristor<br>Silicon | Power<br>Bipolar<br>Silicon | Power<br>MOSFET<br>Silicon | IGBT<br>Silicon | Schottky diode<br>Silicon Carbide | Power HEMT<br>GaN |

It's time to move on...

#### Material Properties Comparison

| Material Property                                    | Silicon | SiC-4H | GaN  |

|------------------------------------------------------|---------|--------|------|

| Band-gap (eV)                                        | 1.1     | 3.2    | 3.4  |

| Critical Field (1E+6V/cm)                            | 0.3     | 3      | 3.5  |

| Electron Mobility (cm <sup>2</sup> /V-Sec.)          | 1450    | 900    | 2000 |

| Electron Saturation Velocity (1E+6 cm/Sec.)          | 10      | 22     | 25   |

| Thermal Conductivity (W/cm²K)                        | 1.5     | 3.8    | 1.3  |

| Baliga Figure of Merit (FOM)= $\epsilon_s \mu E_c^3$ | 1       | 675    | 3000 |

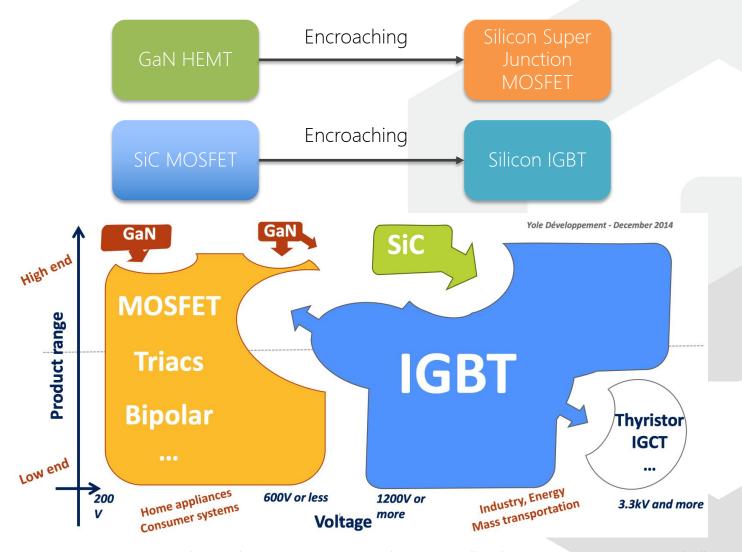

#### WBG Power Devices: Applications

Source: Yole Development: How power electronics will reshape to meet 21st century challenges? ISPSD 2015

# Substrate Materials for GaN HEMT

| Attributes                             | Si sub.   | SiC sub. | Sapphire | GaN sub             |

|----------------------------------------|-----------|----------|----------|---------------------|

| Defect density (cm <sup>-2</sup> )     | 1E+9      | 5E+8     | 3E+8     | 1E+3 to 1E+5        |

| Lattice mismatch (%)                   | 17        | 3.5      | -16      | 0                   |

| Thermal conductivity (W/cm-k at 25 °C) | 1.5       | 4.9      | 0.25     | 1.3                 |

| Coefficients of thermal expansions (%) | 54        | 25       | 34       | 0                   |

| Off-state leakage                      | high      | high     | low      | low                 |

| Reliability and yield                  | low       | low      | low      | high                |

| Lateral or Vertical device             | lateral   | lateral  | lateral  | lateral or vertical |

| Integration possibility                | Very high | Moderate | Moderate | -                   |

| Substrate size (mm)                    | 300       | 150      | 100      | 50                  |

| Substrate cost (relative)              | Low       | high     | Low      | Very high           |

Power

RF

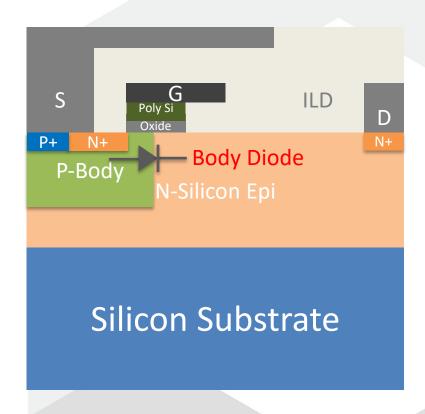

#### Simplified E-GaN vs. LDMOS Device Structures

GaN HEMT

Silicon LDMOS

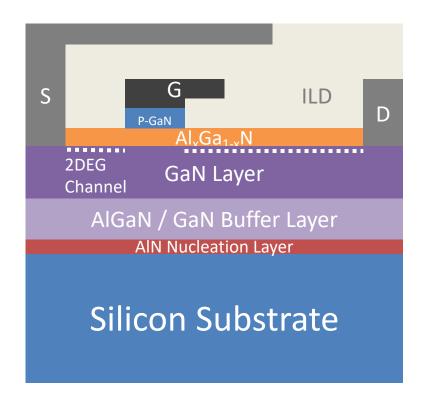

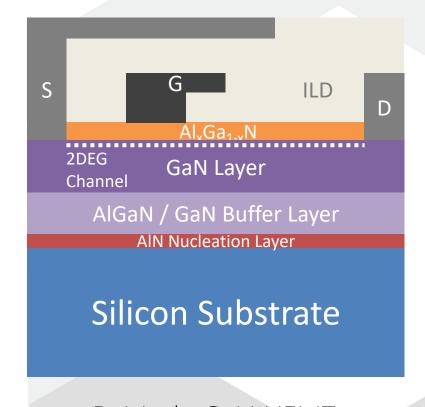

#### Simplified E-Mode vs. D-Mode GaN HEMT

E-Mode GaN HEMT

D-Mode GaN HEMT

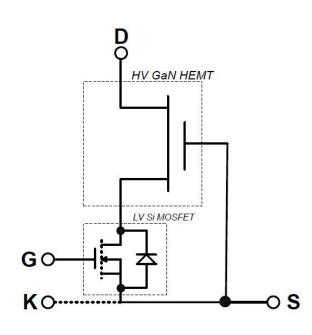

#### Cascode GaN HEMT

#### Good:

- > GaN is normally on by nature: easy to fabricate

- Si like gate control with higher V<sub>th</sub>

- Reverse conduction with LV MOS body-diode

#### Bad:

- Comparatively lower performance

- Controlling silicon rather than GaN gate

- May need extra TVS device to protect MOS

- Difficult to match C<sub>oss</sub> of GaN and MOS

- Still has Q<sub>rr</sub>

|                                 | GaNPower GaN<br>HEMT | Super Junction<br>MOS | SiC      | Cascode GaN |

|---------------------------------|----------------------|-----------------------|----------|-------------|

| Part ID                         | GPI65015TO           | XXXXXXXX              | XXXXXXXX | xxxxxxxx    |

| Rated Voltage                   | 650V                 | 700V                  | 650V     | 600V        |

| R <sub>on</sub>                 | 92mΩ                 | 125mΩ                 | 100mΩ    | 150mΩ       |

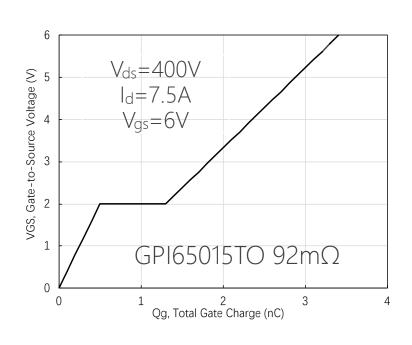

| Qg                              | 3.3nC                | 35nC                  | 51nC     | 6nC         |

| R <sub>on</sub> *Q <sub>g</sub> | 304                  | 4375                  | 5100     | 900         |

#### Cascode GaN HEMT

- Cascode can make package more complicated with 3 components and ceramic substrate

- Can be more expensive than pure Emode

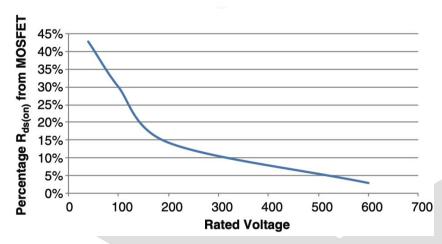

- > Also, cascode is not feasible for low voltage (<200V) GaN, due to the R<sub>dson</sub> portion from MOS is too high:

- > for 600V device, Rdson from MOS contribute less than 5%;

- for 100V device, MOS can contribute more than 30% of the  $R_{dson}$ , which is impractical

1. System Plus Consulating: https://www.systemplus.fr

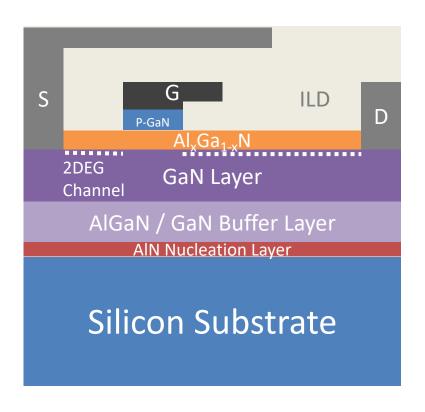

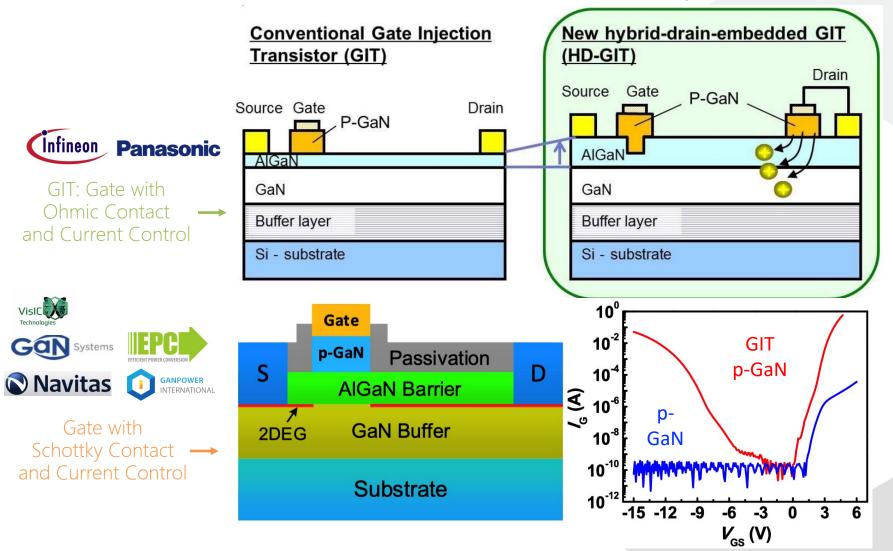

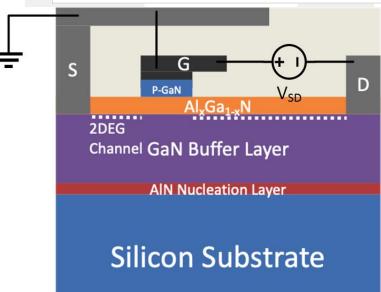

## Commercial E-Mode GaN HEMT with "p-GaN"

<sup>1,</sup> Kevin J. Chen, Understanding the Dynamic Behavior in GaN-on-Si Power Devices and IC's, Integrated Power Conversion and Power Management, 2018

<sup>2 ,</sup> Greco, G., Iucolano, F., & Roccaforte, F. Review of technology for normally-off HEMTs with p-GaN gate. Materials Science in Semiconductor Processing

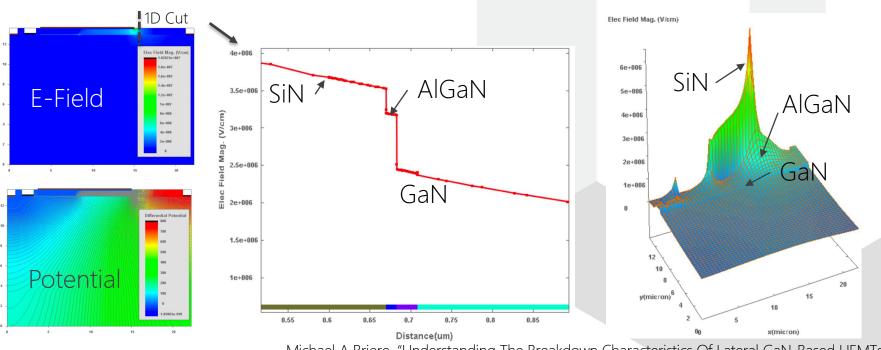

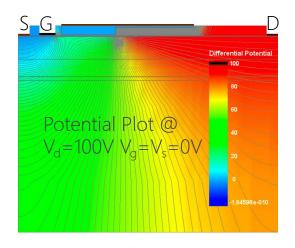

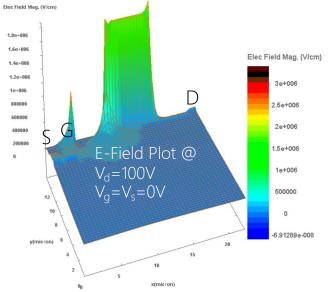

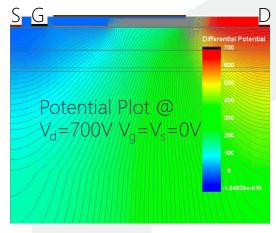

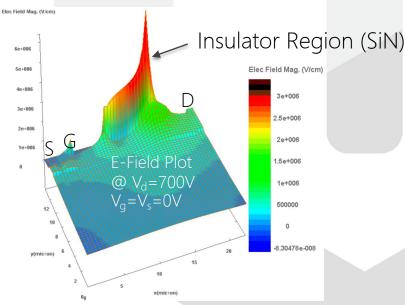

#### Why no Avalanche Breakdown in GaN?

- $\triangleright$  GaN has a very high critical electric field (10 times that of Si, on par with SiO<sub>2</sub> or SiN already)

- > Lateral device structure causes electric field crowding, particularly in overlying insulators

- ➤ GaN HEMT is more like a ceramic capacitor breakdown in the overlying insulators, where peak electric field took place

- > If breakdown ever occurs, the device suffers permanent damage

- Design margin (>30%) for GaN is usually much higher than that of Si (which only has 10%)

Michael A Briere, "Understanding The Breakdown Characteristics Of Lateral GaN-Based HEMTs"

#### Why no P-type GaN HEMT Like PMOS?

- ➤ Si has both NMOS and PMOS, for NMOS, current is carried by electrons while in PMOS, current is carried by the holes

- ➤ However, for GaN HEMT, there is no P-type GaN HEMT yet

- First, ion implantation and subsequent annealing of magnesium in GaN is very difficult to achieve

- > Second, hole mobility in GaN is very low (30 cm<sup>2</sup>/Vs for holes vs. 2000 cm<sup>2</sup>/Vs for electrons)

- ➤ GaN monolithic ICs are realized either by using complementary E-mode and D-mode GaN, or using E-mode GaN only

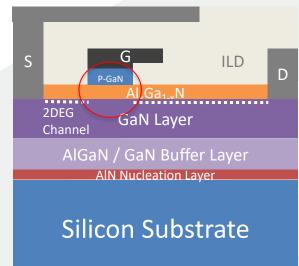

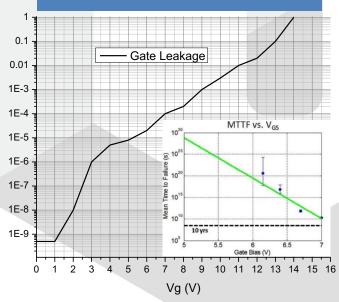

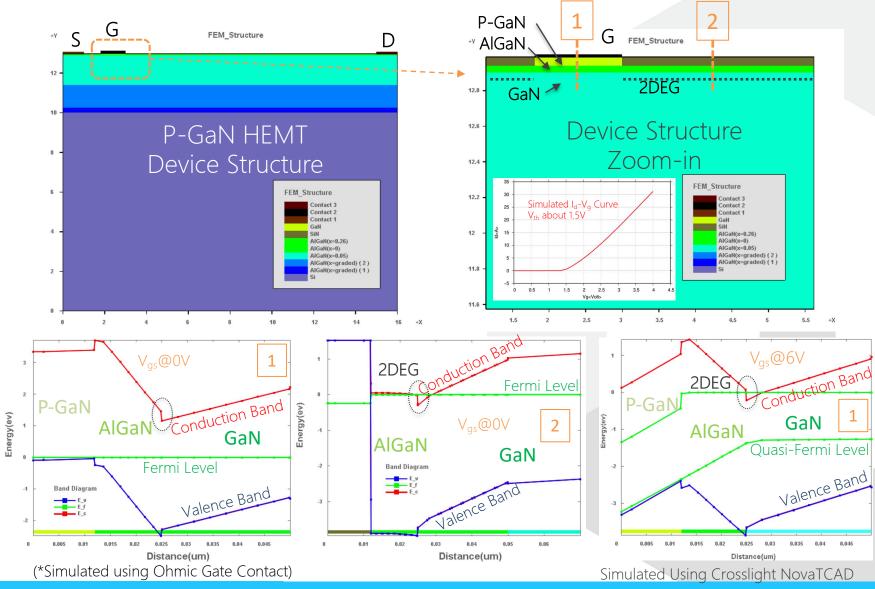

# Why E-mode GaN $V_{g-max}$ is Limited to 7V

- ➤ Unlike a silicon MOS, the P-GaN / AlGaN / GaN can be viewed as a PIN diode structure with a depletion region

- ➤ With in-situ doped p-type dopant (Magnesium) for p-GaN layer, the depletion region extends over the thickness of the GaN 2DEG channel for V<sub>g</sub>=0V, thus interrupts the channel below the gate region

- ➤ When a positive gate bias is applied, the 2DEG channel is re-established, yielding to on-state conditions

- ➤ Gate leakage current increases with increasing gate voltage. Voltage beyond 7V will results higher gate leakage current

- For the P-GaN / AlGaN / GaN gate stack, a TDDB (Time Dependent Dielectric Breakdown) needs to be analyzed for proper max gate voltage with long term reliability concerns

- ➤ It has been determined that maximum rating of 6~7V for p-GaN HEMT is most appropriate

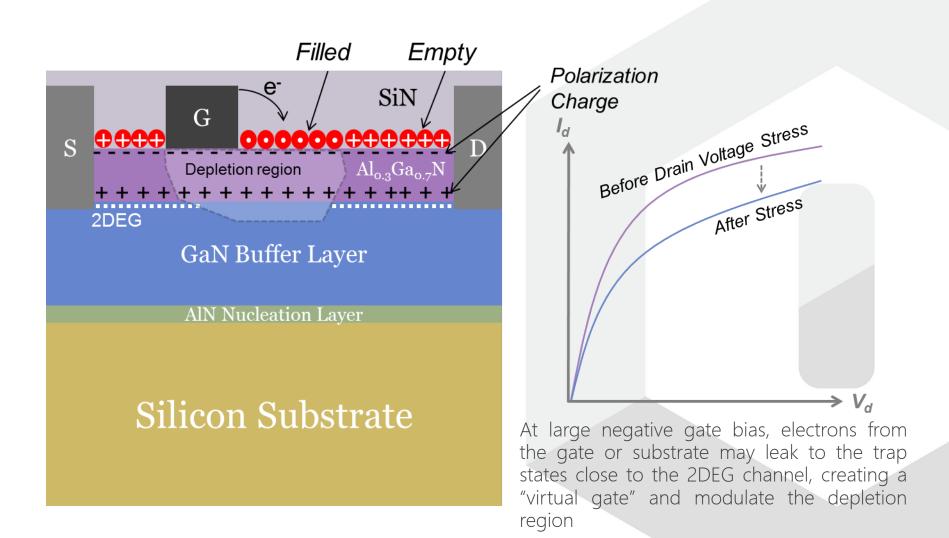

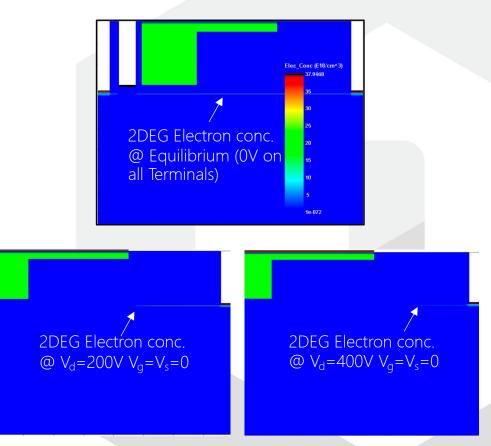

#### Current Collapse Phenomenon

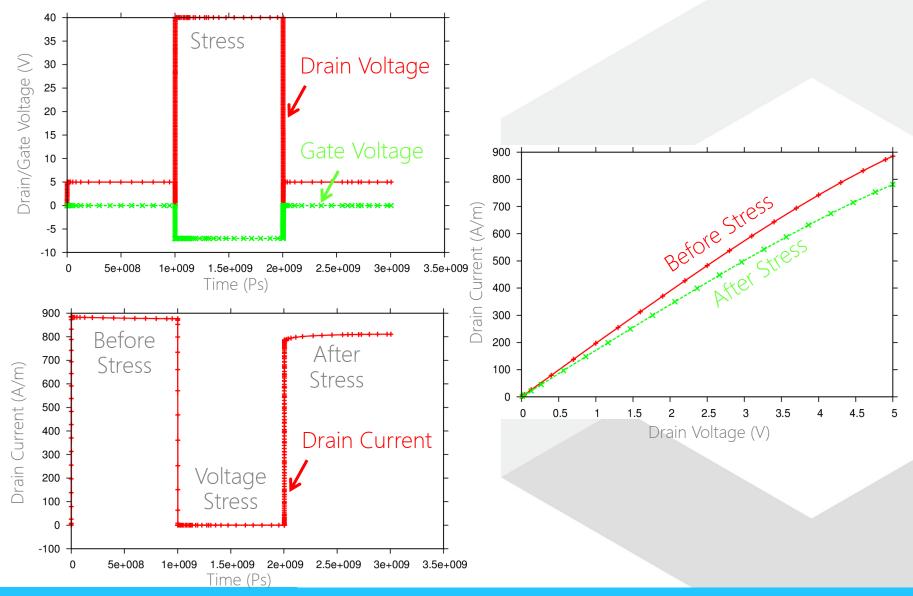

#### Current Collapse: TCAD Transient Simulation

#### Contents

- > Session 1: GaN devices basics

- > GaN, An Introduction

- > GaN Design, Fabrication and Testing

- ➤ GaN Compact Modeling and Reliability

- > Session 2: GaN Gate Driving

- > Session 3: GaN Applications

## GaN Power Device Supply Chain

Basic Semiconductor Materials

GaNPower 6 inch GaN Wafer (real photo)

Final Power Supply Products

Packaged GaN Devices

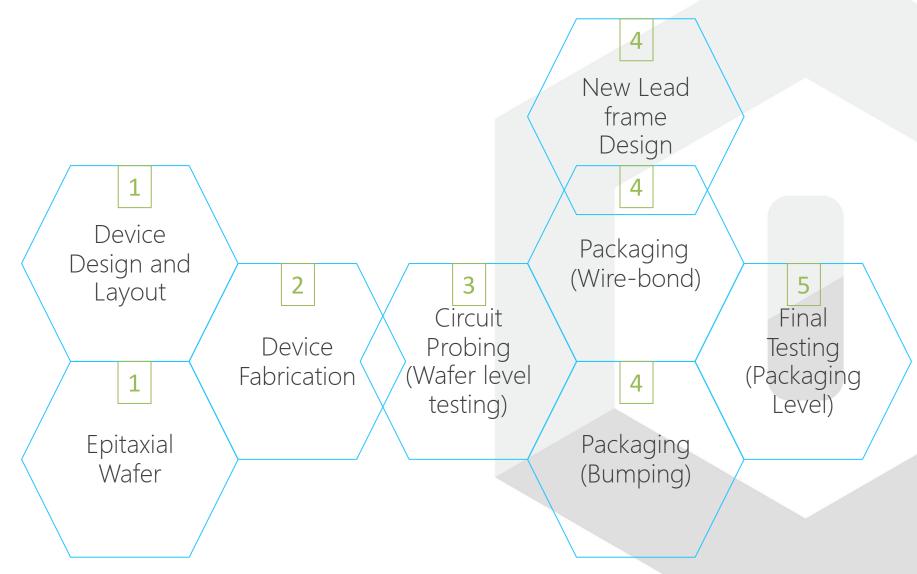

#### How GaN Power Devices Are Fabricated?

Device

Design and

Layout

## GaN Design Stage (TCAD Simulation)

# GaN Design Stage (TCAD Simulation)

Depletion Region Propagates

Simulated Using Crosslight NovaTCAD

#### GaN Design Stage (TCAD Simulation)

Simulated Using Crosslight NovaTCAD

# Device Design and Layout

#### GaN Design Stage (TCAD Simulation)

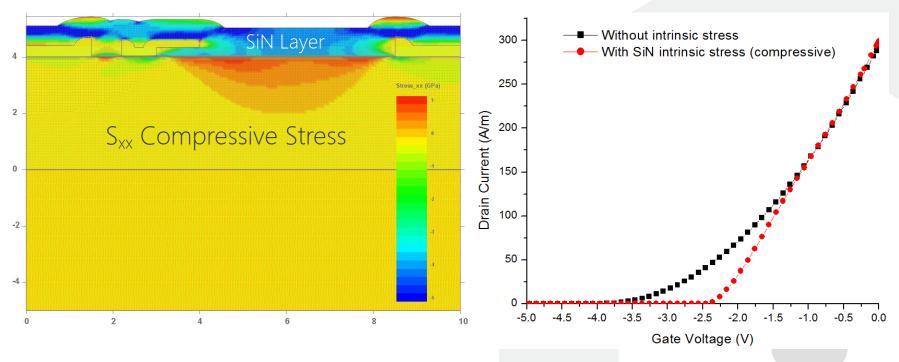

- In addition to stress caused by material lattice mismatch, the intrinsic stress from SiN layer can be defined in the process simulation. The stress profile can be used by the device simulator to calculate the piezoelectric polarization.

- > Stress engineering may help to achieve enhancement mode?

Simulated Using Crosslight NovaTCAD

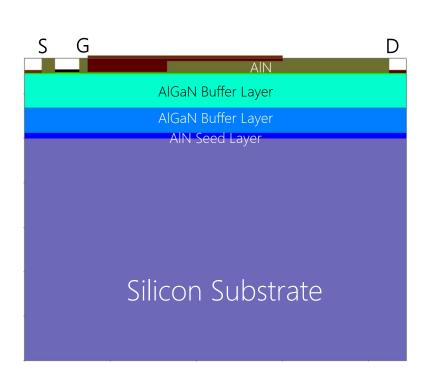

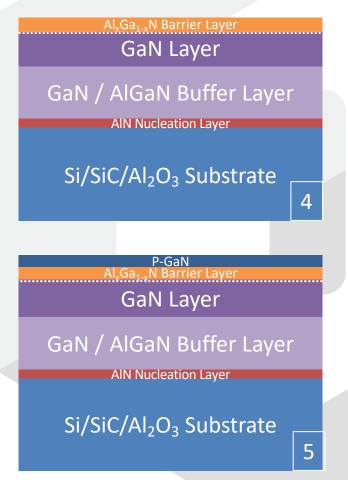

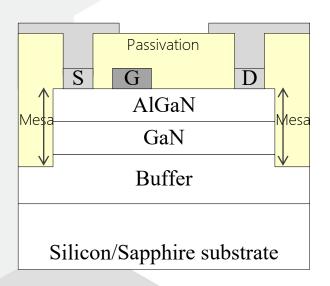

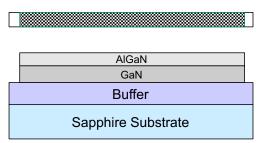

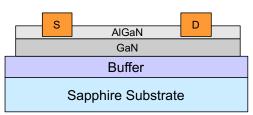

The GaN Epi wafer is fabricated from either Si, SiC or Sapphire substrate. Each layer is deposited using MOCVD (Metal Organic Chemical Vapor Deposition) for low cost and high throughput

Device Fabrication

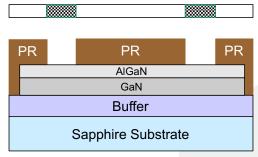

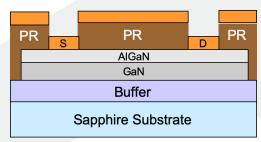

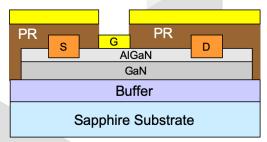

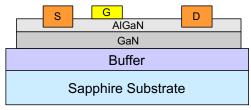

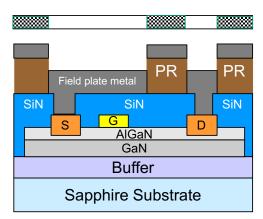

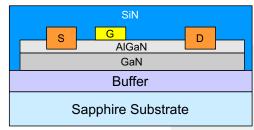

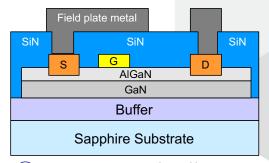

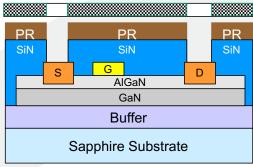

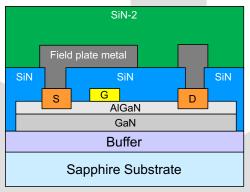

#### A GaN-on-Sapphire HEMT Fabrication Example

## Fabrication Steps (D-mode HEMT)

Simplified GaN-on-Sapphire HEMT Process Flow (GaN-on-silicon is similar):

| 1  | Wafer Cleaning                         |

|----|----------------------------------------|

| 2  | Mask #1: Mesa Etching                  |

| 3  | RIE Mesa Etching                       |

| 4  | Mask #2: S/D Contacts                  |

| 5  | Ohmic Contact Deposition               |

| 6  | Mask #3: Gate Lithography              |

| 7  | Schottky Gate Deposition               |

| 8  | Growth of Passivation Layer            |

| 9  | Mask #4: Contact Hole Opening          |

| 10 | Mask #5: Field plate and metallization |

- ① Mask 01 Mesa etch

- Define a device area

- Create isolation between devices

- (4) Lift-off and Anneal

- To improve contact quality

- Bad annealing may dramatically degrade the device performance

- 2 Mask 02 S/D

- Source and drain contact to AlGaN

- The metal must be deposited after a completely clean process to eliminate layers between AlGaN and Metal

- ⑤ Mask 03 Gate

- Define gate region

- The alignment in this step is the most critical as it affects many parameters (L<sub>gd</sub>, Gate on Mesa, design of field plate)

- 3 Deposit S/D metal

- Deposit ohmic contacts on top of AlGaN as source and drain

- 6 Gate Metal Deposition

- Pre-clean is important for the Schottky barrier

#### A GaN-on-Sapphire HEMT Process Flow Example

⑦ Gate metal Lift-off

Mask 05 – Field Plate

- SiN deposition (passivation)

- The first layer of SiN layer is for passivation

- It is important for decreasing the traps at the AlGaN surface

- Many device performances, including leakage current, threshold voltage, breakdown voltage, are related to the quality of this passivation

- This layer is also used for the field plates

Field Plate Lift-off

- Mask 04: S/D contact

- ➤ The source fingers are opened for field plates

- The S/D/G pads are opened

- All other area should be covered by SiN

- 12 Second SiN deposition

- covers the whole area

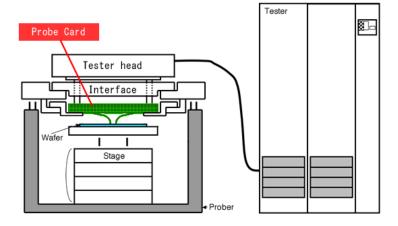

#### Circuit Probing (Wafer level testing)

## Circuit Probing (CP)

Probe Card

https://www.mjc.co.jp/en/technology/ http://www.jemam.com/probecard.htm https://www.formfactor.com/ http://www.jem-net.co.jp/en/products/pro\_hando\_top.html Circuit Probing can sort out bad dies from good dies by combining multiple test items, both room temperature and high temperature tests can be applied

#### Test items example:

- ✓ I<sub>dss</sub>: Drain leakage current

- ✓ I<sub>gss</sub>: Gate leakage current

- ✓ V<sub>th</sub>: Threshold voltage

- ✓ R<sub>dson</sub>: On-state resistance

- ✓ g<sub>m</sub>: Transconductance

Pass / Fail depends on specified range, bad dies are inked to avoid being picked up for further packaging

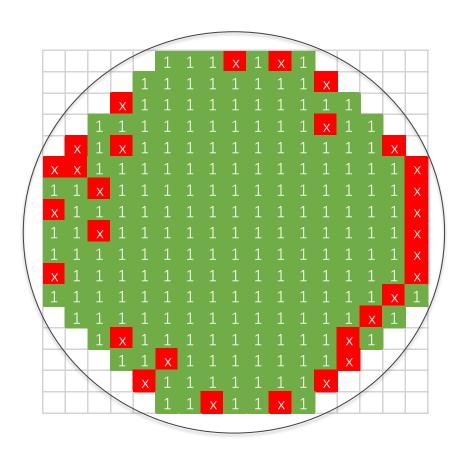

#### Circuit Probing (CP)

Failed sites are marked with ink and will not be picked for packaging afterwards

In this example, we have:

- ✓ Total dies: 229

- ✓ Bad dies: 32

- ✓ Yield: 86%

Sometimes the CP specs are too tight, resulting lower yield. But a too loose spec can lead to increased device early failures

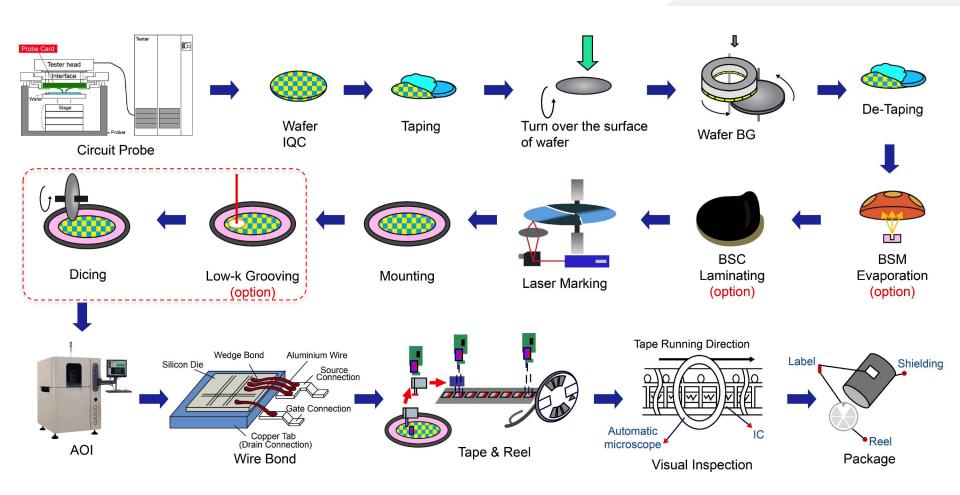

# Packaging (Wire-bond)

## Simplified Packaging Steps

#### Final Test (FT)

Power device FT tester

Final test can identify problems with assembled devices, and it is the last test before shipment

#### Test items example:

- ✓ I<sub>dss</sub>: Drain leakage current

- ✓ V<sub>th</sub>: Threshold voltage

- ✓ R<sub>dson</sub>: on-state resistance

- ✓ BV: Breakdown voltage

Pass / Fail depends on specified range

http://www.accotest.com/index.asp

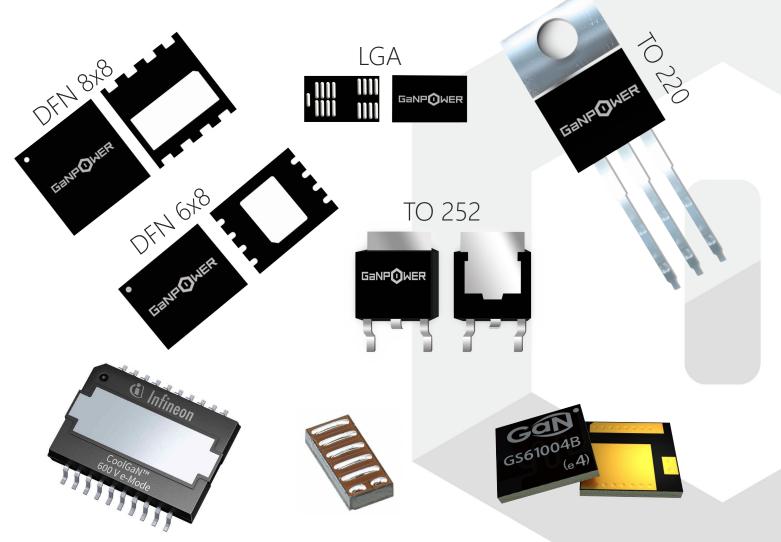

# GaN Packaging Types

## GaN Device Parameter Testing

- ✓ Static (DC) parameters testing

- Rdson, Vth, BV, Idss, Igss, Vsd, Rg, etc...

- ✓ Dynamic parameters testing

- Ciss, Crss, Coss, Qg, Qgs, Qgd, Qrr, etc...

- ✓ Double pulse testing (for dynamic parameters)

- > T<sub>n</sub> T<sub>f</sub>, T<sub>d</sub>, dv/dt, etc...

- ✓ Thermal testing

- > R<sub>thjc</sub>, R<sub>thja</sub>, etc...

- ✓ SOA testing

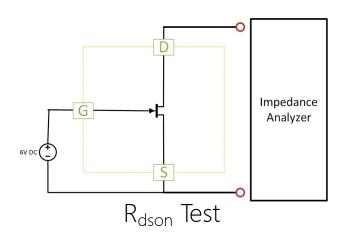

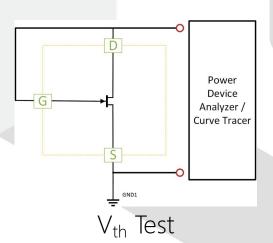

#### Parameter Testing: DC Parameters

- ✓ Static (DC) parameters testing for GaN HEMTs

- Arr R<sub>dson</sub> is tested by applying a 6V gate bias, Kelvin connection should be applied if an impedance analyzer or a power device analyzer/curve tracer such as Keysight 1505A is used. Both room and high temperature R<sub>dson</sub> can be recorded at certain drain current level (e.g. I<sub>d</sub>=5A for 100 m $\Omega$  device)

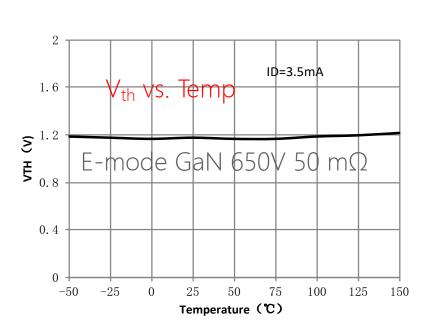

- $ightharpoonup V_{th}$  is tested by shorting drain and gate terminals and apply a voltage to the drain with respect to the source. The voltage is recorded at certain drain current level (e.g. 3.5 mA for 100 m $\Omega$ )

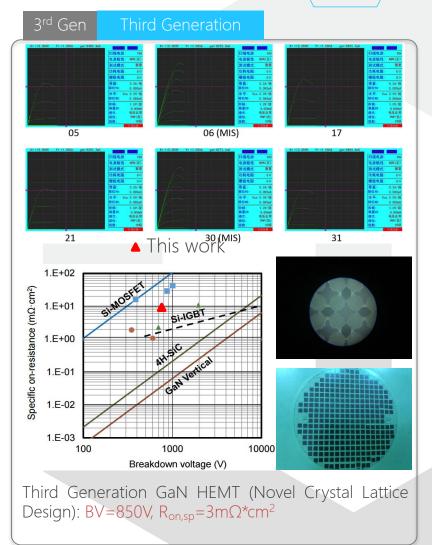

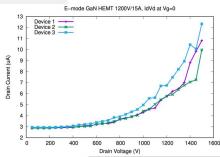

#### Parameter Testing: DC Parameters

- ✓ Static (DC) parameters testing for GaN HEMTs

- ▶ BV (breakdown voltage test) for GaN HEMT is very different from MOSFET. For I<sub>d</sub>-V<sub>d</sub> breakdown curves are rarely seen in the datasheet. Unlike silicon MOSFET, GaN doesn't have avalanche breakdown. Once GaN device breakdown, the device is destroyed, and the equipment is likely not fast enough to catch the complete curves

- ➤ GaNPower's 650V E-mode devices real breakdown voltage is above 900V for a safety margin

- ➤ GaNPower is also the world's first and only provider of 1200V single chip E-mode GaN HEMT, with real breakdown voltage exceeding 1500V

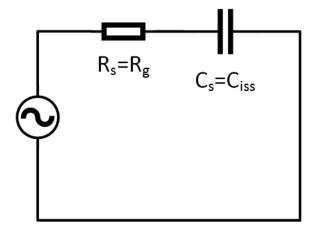

# Parameter Testing: R<sub>g</sub>

Gate internal resistance is measured with drain open and high frequency, such as f=25MHz

$$V(t) = V_{bias} + V_{o} \sin \omega t$$

$$I(t) = I_{o} \sin(\omega t + \theta)$$

$$I_{o} = \frac{V_{o}}{\sqrt{R^{2} + (\frac{1}{\omega C})^{2}}}$$

$$\theta = \tan^{-1} \frac{1}{R\omega C}$$

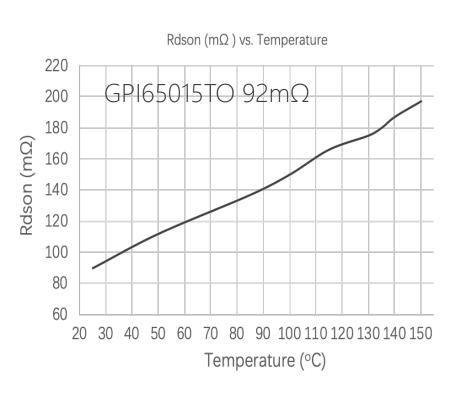

### Parameter Testing: R<sub>dson</sub> vs. Temp

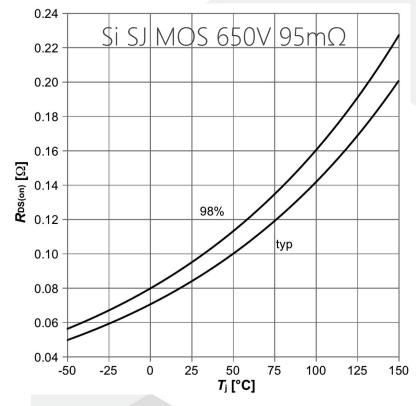

For GaN HEMT:  $R_{dson}$  temp ratio:  $R_{dson(T=25C)}/R_{dson(T=150C)} = 195 m\Omega/92 m\Omega = 2.12$

For SJ MOS:  $R_{dson}$  temp ratio:  $R_{dson(T=25C)}/R_{dson(T=150C)}=200 m\Omega/90 m\Omega=2.17$

R<sub>dson</sub> temperature ratio of GaN HEMT and SJ MOS are on par

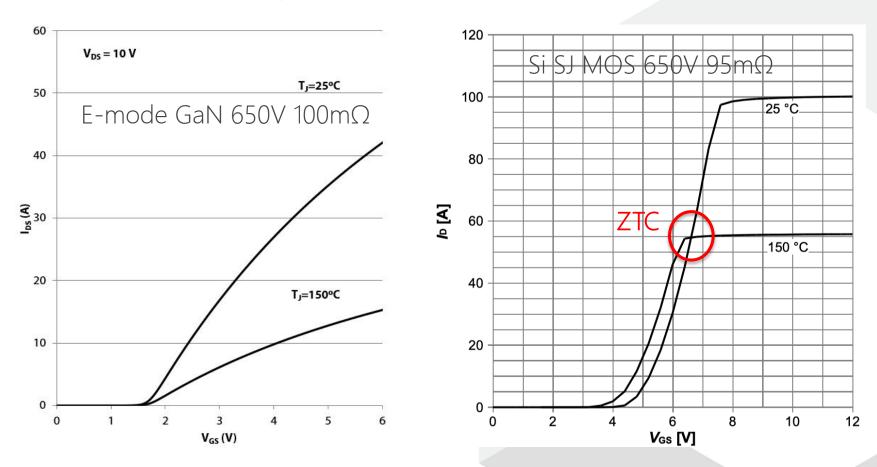

## Parameter Testing: I<sub>D</sub> vs. V<sub>GS</sub>

For silicon SJ MOS, a Zero Temperature Coefficient (ZTC) point exists. Below this point, current increases with increasing temperature, causing hot spot and device failure. E-mode GaN has no such issue

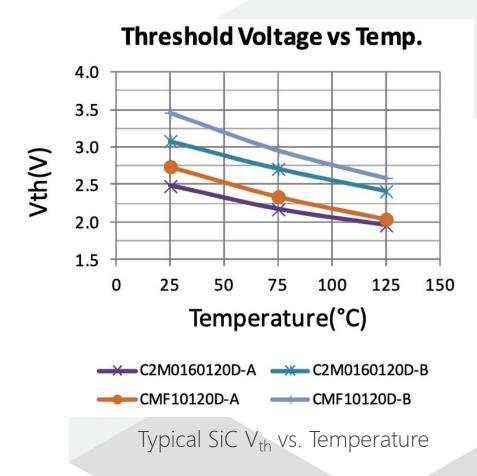

## Parameter Testing: V<sub>th</sub> vs. Temp

Typical GaN V<sub>th</sub> vs. Temperature

Gangyao Wang, John Mookken, Julius Rice, Marcelo Schupbach: Dynamic and Static Behavior of Packaged Silicon Carbide MOSFETs in Paralleled Applications, IEEE https://www.richardsonrfpd.com/docs/rfpd/Dynamic\_and\_Static\_Behavior\_SiC\_MOSFET.pdf

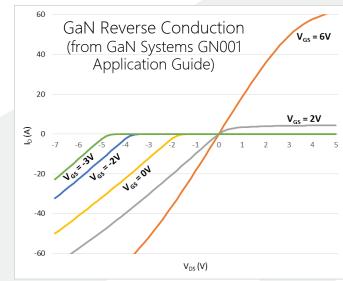

Parameter Testing: Reverse Cond. and V<sub>sd</sub>

- > There is no PN junction in the GaN device

- With S and G connected, applying a negative V<sub>DS</sub> equals to applying a positive V<sub>GD</sub>

- ➤ When V<sub>GD</sub> exceeds the threshold voltage, the channel will conduct current, much like the body-diode of a MOSFET

- ➤ A negative bias on the Gate terminal requires an equal potential drop on the drain terminal so that V<sub>GD</sub> can reach V<sub>th</sub>

- In datasheet,  $V_{sd}$  is usually larger than  $V_{th}$  because the test criteria of  $I_d$  (for  $V_{th}$ ) and  $I_s$  (for  $V_{sd}$ ) is different.  $V_{sd}$  is usually defined at a much higher current value than  $V_{th}$

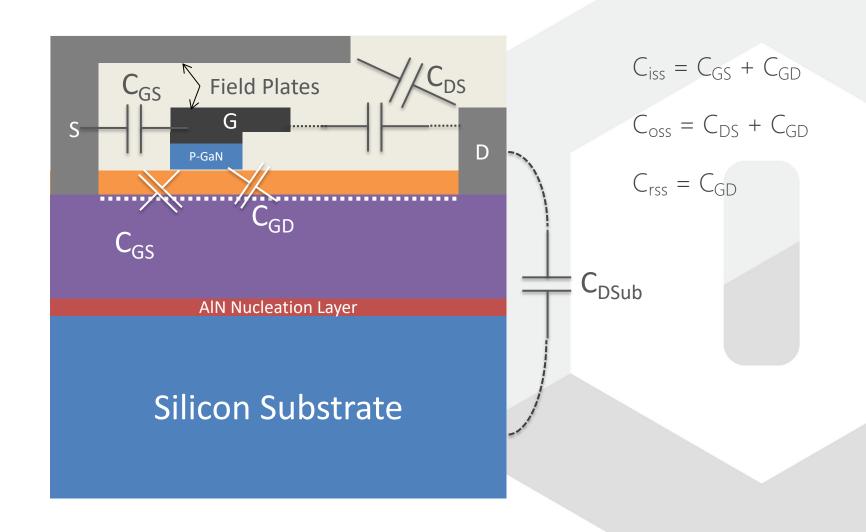

## Parameter Testing: Capacitance

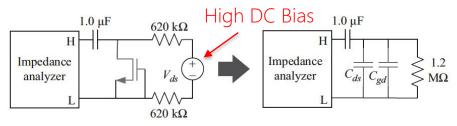

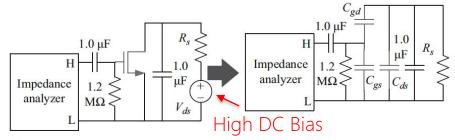

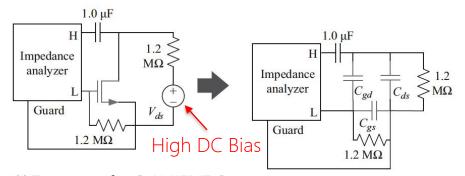

#### Parameter Testing: Capacitance

(a) Test setup for GaN HEMT Coss

(b) Test setup for GaN HEMT Ciss

(c) Test setup for GaN HEMT  $C_{rss}$

$$C_{oss} = \frac{C_{isolation}C_{measured}}{C_{isolation} - C_{measured}}$$

$$C_{measured} \ll C_{isolation} = 1uF$$

;  $C_{measured} \sim pF \ range$

$$C_{oss} \approx C_{measured}$$

$$C_{iss} = \frac{C_{isolation}C_{measured}}{C_{isolation} - C_{measured}}$$

$$C_{measured} \ll C_{isolation} = 1uF$$

;  $C_{measured} \sim pF$  range

$$C_{iss} \approx C_{measured}$$

$$C_{rss} = \frac{C_{isolation}C_{measured}}{C_{isolation} - C_{measured}}$$

$$C_{measured} \ll C_{isolation} = 1uF$$

;  $C_{measured} \sim pF \ range$

$$C_{rss} \approx C_{measured}$$

Fei (Fred) Wang, Zheyu Zhang, and Edward A. Jones: Characterization of Wide Bandgap Power Semiconductor Devices, The Institution of Engineering and Technology 2018

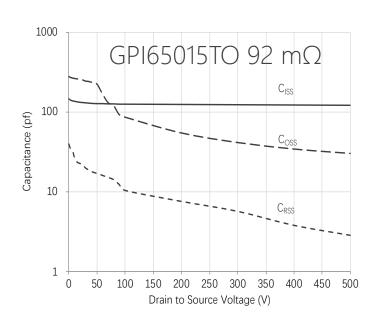

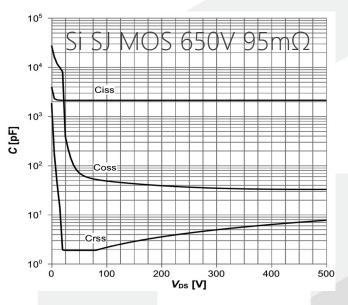

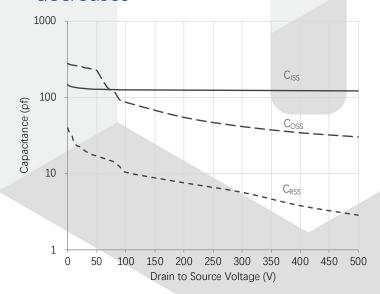

### Capacitance: Si SJ MOS vs. GaN

For GaN HEMT:  $C_{OSS}$  variation:  $C_{oss(Vds=0.5V)}/C_{oss(Vds=500V)} = 521 pF/30 pF = 17.4$

For Si SJ MOS:  $C_{OSS}$  variation:  $C_{oss(Vds=0.5V)}/C_{oss(Vds=500V)} = 2.8 \times 10^4 pF/32 pF = 875$

Silicon SJ MOSFET has a much wider  $C_{oss}$  variation, which causes significant non-linearity -> more severe EMI

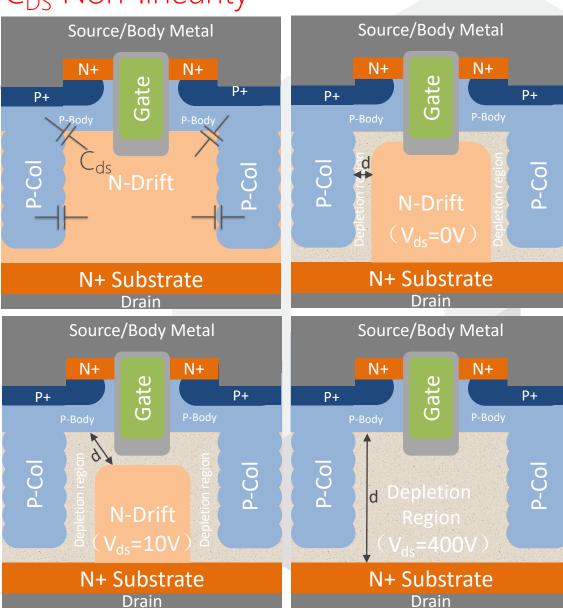

#### Super Junction MOS C<sub>DS</sub> Non-linearity

C<sub>ds</sub> can be calculated as:

$$C_{\rm ds} \propto \frac{\varepsilon A}{d}$$

- A is the total area formed by the P/N junction depletion region, d is depletion width

- For small  $V_{ds}$ , A is large, and d is narrow, so  $C_{ds}$  is large

- With increasing V<sub>ds</sub>, d increases while A keeps almost constant, C<sub>ds</sub> decreases

- At certain V<sub>ds</sub>, the lateral depletion regions merge, A suddenly drops, and d is wide, C<sub>ds</sub> decreases significantly

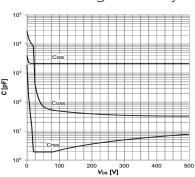

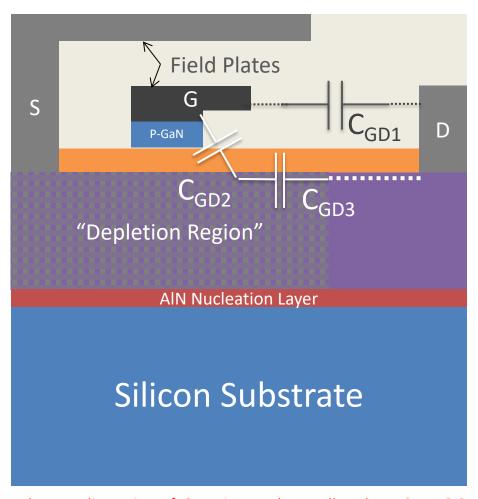

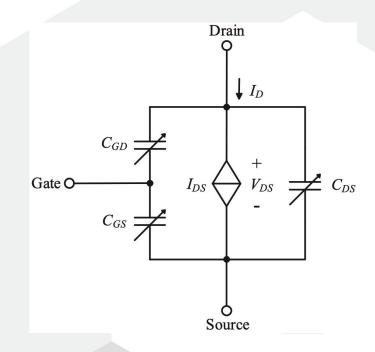

### GaN C<sub>GD</sub> Non-linearity

The nonlinearity of GaN is much smaller than SJ MOS in terms of  $C_{GD}$  and  $C_{DS}$

$ightharpoonup C_{GD}$  of GaN can be viewed as  $C_{GD2}$  and  $C_{GD3}$  in series and  $C_{GD1}$  in parallel:

$$C_{GD} = C_{GD1} + \frac{C_{GD2}C_{GD3}}{C_{GD2} + C_{GD3}}$$

With a high  $V_{DS}$  applied, while  $C_{GD1}$  and  $C_{GD2}$  are not sensitive to  $V_{DS}$ ,  $C_{GD3}$  decreases with the increasing depletion region, causing  $C_{GD}$  to decreases

# Capacitance: $C_{o(er)}$ and $C_{o(tr)}$

- Coss is voltage dependent, no matter GaN or SJ MOS

- ➤ Single point C<sub>oss</sub> value is not very useful, it can't represent the entirety of the capacitance curve

- > By using the energy and time related effective output capacitance values, calculations will be more accurate, and they are more convenient to use

- These output capacitances ( $C_{o(er)}$  and  $C_{o(tr)}$ ) are usually evaluated at 80% of rated breakdown voltage (80% BVdss, or BV<sub>80%</sub>)

- $\triangleright$  The energy related effective output capacitance  $C_{o(er)}$  and time related effective output capacitance  $C_{o(tr)}$  can be calculated using the following equations:

$$C_{o(tr)} = \frac{Q_{oss-80\%}}{BV_{80\%}} = \frac{\int_0^{BV_{80\%}} C(V)dV}{BV_{80\%}}$$

$$C_{o(er)} = \frac{2}{BV_{80\%}^2} = \int_0^{BV_{80\%}} C(V)VdV$$

Alexander J. Young, ON Semiconductor, Characterizing the dynamic output capacitance of a MOSFET

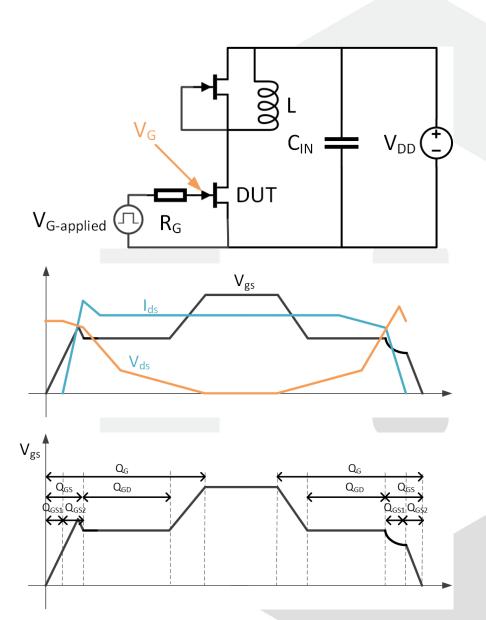

# Parameter Testing: Q<sub>g</sub>

- Q<sub>g</sub> can be tested with single pulse inductive load switching

- The value of  $R_G$  is intentionally chosen to be large (>300 $\Omega$ ) so that the switching transient can be slowed down for better calculation

- Q<sub>g</sub> can then be extracted as (for Turn-off):

$$I_{G}(t) = \frac{V_{G}(t) - V_{G-applied}(t)}{R_{G}}$$

$$Q_{G}(V_{G}) = \int_{0}^{t} \frac{V_{G}(t) - V_{G-applied}(t)}{R_{G}} dt$$

$$Q_{GS} = Q_{G} (V_{G} = V_{Plateau})$$

$$Q_{GD} = Q_{G(V_{D}=0)} - Q_{G(V_{D}=VDD)}$$

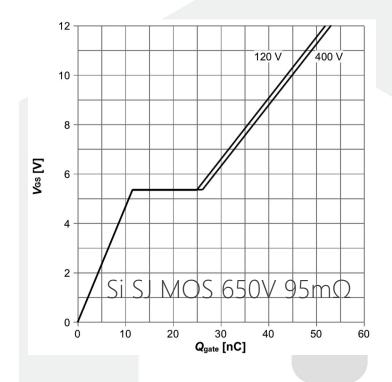

## Parameter Testing: Q<sub>q</sub> Curve

GaN  $Q_g$  is one order of magnitude smaller compared to silicon SJ MOS with similar  $R_{dson}$  and BV ratings

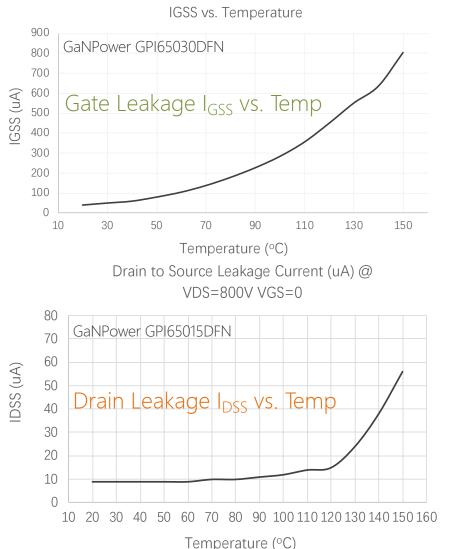

# Parameter Testing: I<sub>dss</sub> and I<sub>gss</sub> vs. Temp.

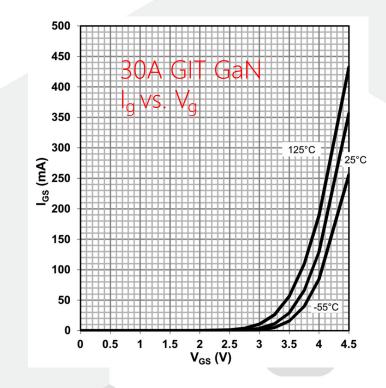

A GIT device, such as GaN offered by Panasonic and Infineon, exhibits a much higher gate current, since they are current driven, rather than voltage driven GaN devices, like BJTs

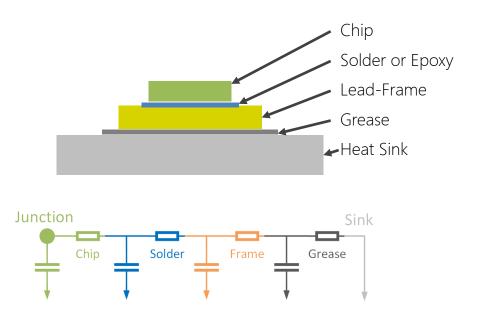

## Current Collapse: Dynamic R<sub>dson</sub>

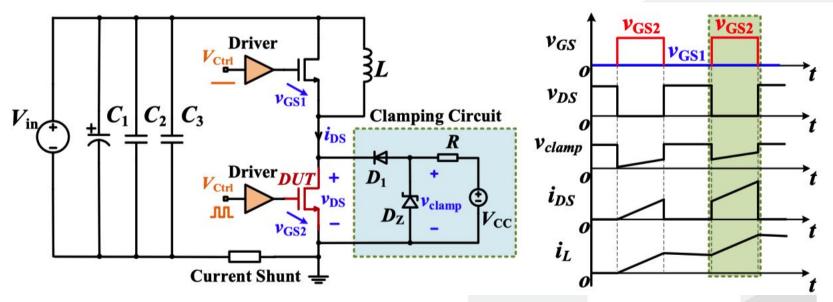

- ➤ There are various ways to measure dynamic R<sub>dson</sub>, most of these methods involve a fast and accurate clamping circuit

- In this setup, the voltage drop  $V_{clamp}$  across the Zener diode  $D_Z$  is measured instead of  $V_{DS}$ , the diode forward voltage  $V_{D1}$  is calibrated so that low  $R_{dson}$  of GaN can be accurately measured

- $\triangleright$  R is chosen to limit the current of D<sub>1</sub> so that it won't heat-up

Source: Rui Li, Xinke Wu, Gang Xie, Kuang Sheng, Dynamic On-state Resistance Evaluation of GaN Devices under Hard and Soft Switching Conditions, APEC 2018

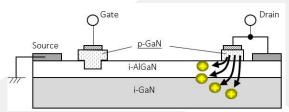

## Current Collapse: Dynamic R<sub>dson</sub>

| Parameters                       | Device A               | Device B              | Device C              |  |

|----------------------------------|------------------------|-----------------------|-----------------------|--|

| Voltage/Curre<br>nt Rating       | 600V/13A               | 650V/30A              | 600V/35A              |  |

| Technology                       | E-mode<br>(X-GaN GIT)  | E-mode (p-gate)       | $CoolMOS^{TM}$        |  |

| Package                          | DFN 8×8                | GaNPX™ 4              | TO-220                |  |

| $\mathbf{R_{DSON}}^{\mathrm{a}}$ | $140 \mathrm{m}\Omega$ | $50 \mathrm{m}\Omega$ | $60 \mathrm{m}\Omega$ |  |

hybrid-drain- embedded-GIT. The hole injection from the additional drain-side p-GaN at the OFF state compensates the electron trapping in the epilayer. Successfully suppressed current collapse up to 850 V was obtained. (K.Chen IEEE TED 2017)

Technology has improved over the past two years, the dynamic R<sub>dson</sub> is better now than 2 years ago

Source: Rui Li, Xinke Wu, Gang Xie, Kuang Sheng, Dynamic On-state Resistance Evaluation of GaN Devices under Hard and Soft Switching Conditions, APEC 2018

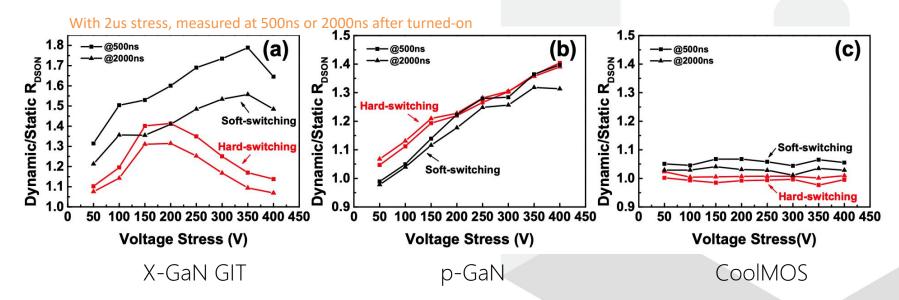

### Parameter Testing: Thermal Resistance

- To test the thermal resistance, we need to know the accurate junction temperature within the packaged device. (We can test the junction temperature using thermal imager or thermal coupler, but it needs to teardown the case)

- For MOSFET with PN junctions, body diode forward voltage  $V_f$  is monitored for sensing the junction temperature. GaN has no body diode. Instead,  $R_{dson}$  is used to sense the  $T_i$ , which means  $T_i = T_i(R_{on})$

# R<sub>thJC</sub> from Various Packaging Forms

|              | Package<br>Type | R <sub>dson</sub> | Material | R <sub>thJC</sub> |

|--------------|-----------------|-------------------|----------|-------------------|

| IPP65R065C7  | TO220           | 65mΩ/33A          | Si       | 0.73 K/W          |

| IPL65R070C7  | ThinPAK 8x8     | 70mΩ/28A          | Si       | 0.74 K/W          |

| IPW60R060P7  | TO247           | 60mΩ/48A          | Si       | 0.76 K/W          |

| IPB65R065C7  | TO263           | 65mΩ/33A          | Si       | 0.73 K/W          |

| IGLD60R070D1 | DFN 8x8         | 70mΩ/15A          | GaN      | 1.1 K/W           |

All data from Infineon datasheet

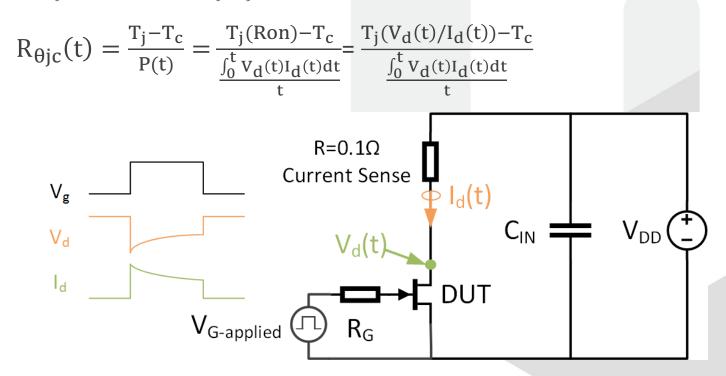

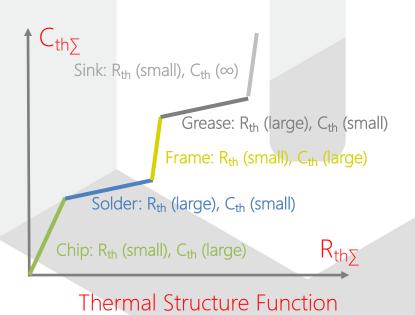

#### Parameter Testing: Thermal Impedance

- > Thermal resistor determines how much power it will dissipate for certain temperature change, while thermal capacitor governs the thermal capacity, or how much heat it can hold on

- Sometimes in Failure Analysis, we use thermal impedance as a guideline for damage caused by either Temperature Cycling (TC) or Power Cycling (PoC). TC tests how the external temperature impact device life-time, while PoC tests how the self-heating gradually damage the device internally

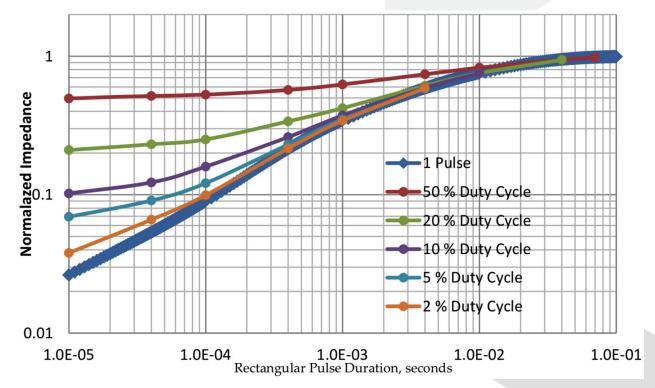

#### Parameter Testing: Transient Thermal Impedance

- > DC thermal impedance is the maximum thermal impedance at steady state

- The transient thermal impedance is a measure of how the device behaves when pulsed power is applied to it. This is important for determining the behavior of low duty cycle, low frequency pulsed loads

- For the same power level, at short durations, the thermal impedance appears to be smaller

GaN systems: Transient thermal modeling of gallium nitride devices (http://tesint.com/docs/Transient\_Thermal\_Modeling\_of\_Electronic\_Devices\_Using\_ElectroFlo.pdf)

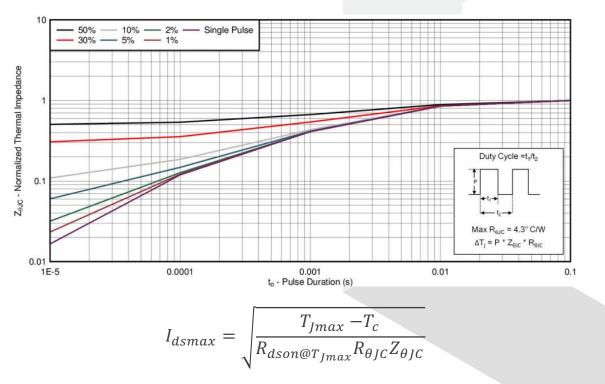

#### How to Rate Continuous Current?

$$\frac{1}{2}I_{dsmax}^{2}R_{dson@T_{Jmax}} = \frac{T_{Jmax} - T_{c}}{R_{thJc}}$$

$$I_{dsmax} = \sqrt{\frac{T_{Jmax} - T_{c}}{R_{dson@T_{Jmax}}R_{thJc}}}$$

- ➤ I<sub>ds</sub> calculated from this method reflects the upper current limit. To keep a safety margin, the current rating is usually lower than the calculated value

- As an example, for CoolMOS IPB65R095C7, R<sub>dson@TJmax</sub>=0.202, R<sub>thJC</sub>=0.98, I<sub>dsmax</sub> from the above equation calculated as 25.13A. This device is rated as 24A by Infineon

- Another current limiting factor is bond wire fusing. But most of the time bonding wires fuse only when devices fail

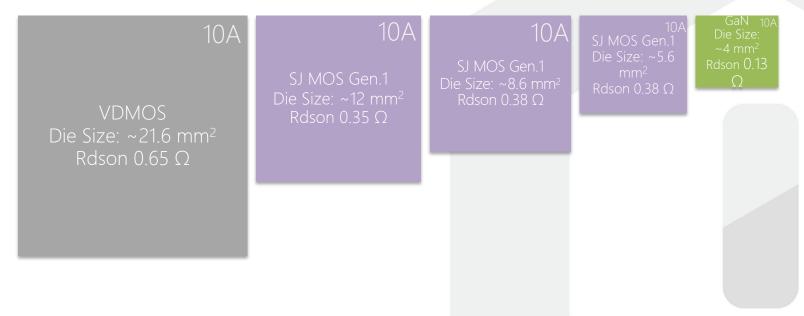

#### Why GaN has a lower current rating with same R<sub>dson</sub>?

- With the same packaging forms and similar  $R_{dson}$ , the continuous current of GaN is rated much lower than silicon, due to the fact that with the same  $R_{dson}$ , GaN chip size is usually much smaller than silicon counter part, which increases thermal resistance  $R_{thIC}$

- As an example, for a GaN device with R<sub>dson@TJmax</sub>=0.26Ω, R<sub>thJC</sub>=1.0K/W, I<sub>dsmax</sub> from the above equation calculated as 22A. This device is rated as 15A by the GaN manufacturer for some safety margins

- Also, the total area of lead-frame bonding pads determine how many bonding wires with certain thickness (1mil, 2mil?) can be applied. These bonding wires have limited current handling capabilities and can be the bottleneck for some packaging types (such as DFN)

- For GaN manufacturers such as GaNPower, we use the same chip in different packaging forms (such as TO220, DFN, etc...), the current ratings are always less meaningful than R<sub>dson</sub> values

#### How to Rate Pulsed Current

- The rating of max pulsed current is similar to that of a continuous current in that both current ratings are calculated rather than tested.

- The pulsed current rating is based on the current pulse duration and duty cycle specified (e.g. 100us duration and duty cycle=1%), with regard to the transient thermal impedance

https://e2e.ti.com/blogs/b/powerhouse/archive/2015/06/29/understanding-mosfet-data-sheets-part-4-mosfet-switching-times

## Chip Sizes Compared

- > SJ Chip size shrinks during the past 20 years. However, GaN is a quantum leap, even with lateral structures.

- > Smaller chip size means lower cost for the same technology

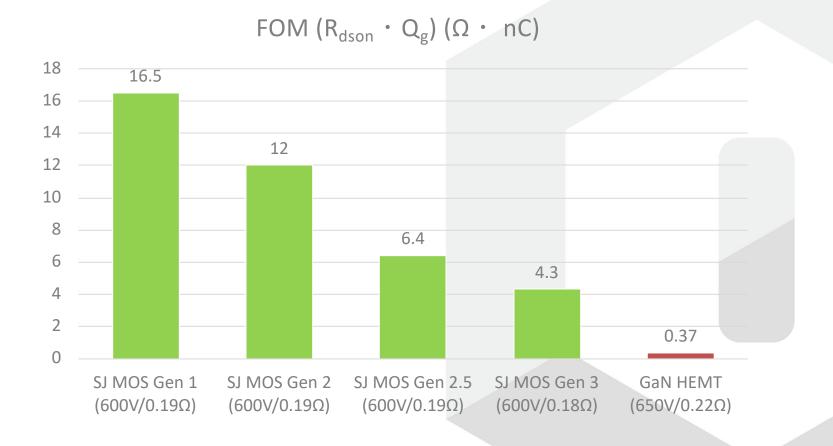

### FOM Comparison (SJ MOS vs. GaN)

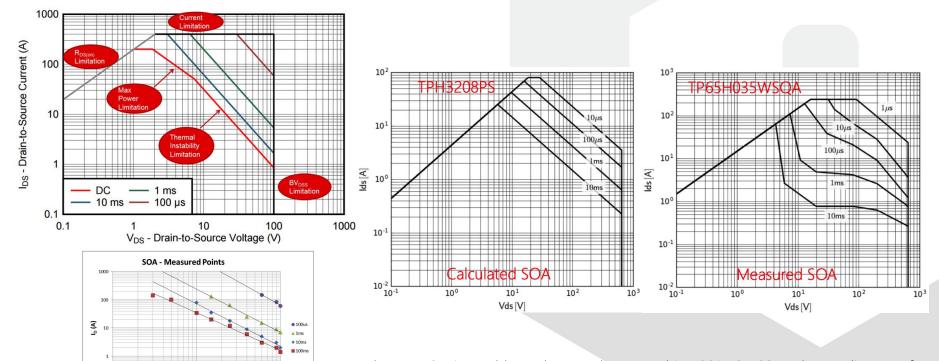

## Parameter Testing: SOA

- GaN has similar SOA definition as Silicon devices

- The thermal instability region indicates where thermal runaway can occur, and the steeper the slope, the more prone the FET is to enter this thermal runaway condition at higher breakdown voltages

- > TLP (Transmission Line Pulse) can be used to test the device SOA boundary

https://e2e.ti.com/blogs\_/b/powerhouse/archive/2015/05/02/understanding-mosfetdata-sheets-part-2-safe-operating-area-soa-graph Datasheet www.transphormusa.com

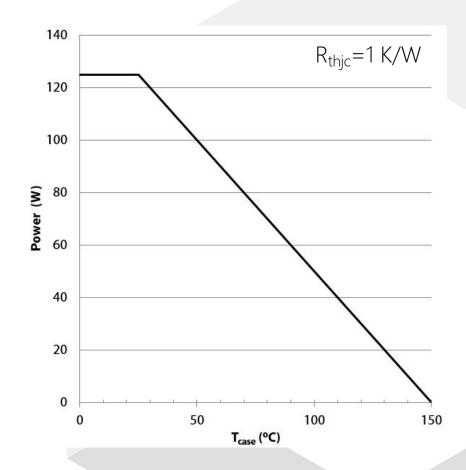

## Parameter Testing: Power Ratings

➤ With R<sub>thJC</sub> available, we can use this equation to calculate the max power allowed:

$$P_{max} = \frac{T_{Jmax} - T_c}{R_{thJC}}$$

A power vs. case temperature curve can then be drawn based on the equation above

Reference: GaN Systems Datasheet

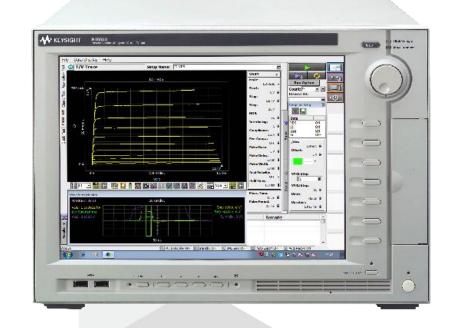

## Datasheet Testing: Keysight B1505A/B1506A

- ➤ Keysight 1500 series is a one stop power device parameter testing platform, with All-in-one solution for power device characterization up to 1500A/10kV

- ✓ Fully automated Capacitance (C<sub>iss</sub>, C<sub>oss</sub>, C<sub>rss</sub>, etc.) measurement at up to 3000V of DC bias

- ✓ Gate charge measurement

- ✓ High voltage/high current fast switch option to characterize GaN current collapse effect

- ✓ Perform both hot and cold temperature dependency testing in an interlock equipped test fixture

Source: https://www.keysight.com/

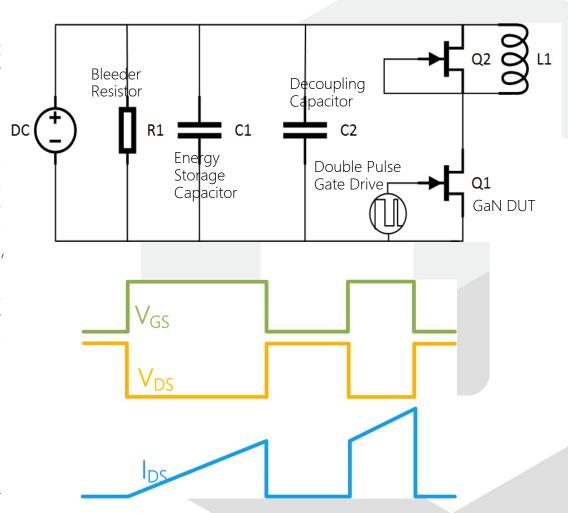

#### Double Pulse Tests: Methods

- The load inductor is used to establish the desired current during the first pulse and keep this current nearly constant during the subsequent turnoff and turn-on transients.

- The capacitors are employed to maintain a stable DC bus voltage. Bulk capacitors with large capacitance supplies energy to establish the inductive current during the first pulse, while the decoupling capacitor with low parasitic equivalent series inductance (ESL) is responsible for supplying transient current during the switching transition.

- ➤ A bleeder resistor is introduced across the DC bus to dissipate the remaining energy stored at the DC capacitors

- The DPT signals are generated either by a signal generator or by a MCU

Source: Fei (Fred) Wang, Zheyu Zhang, and Edward A. Jones, Characterization of Wide Bandgap Power Semiconductor Devices; published by The Institution of Engineering and Technology 2018

### Double Pulse Tests: Descriptions

- ➤ With a constant voltage and a given inductor in the test, there is a constant current change rate di/dt during turn-on.

- The width of the first pulse is set to achieve the current you want to observe, for device characterization this often is the device's rated current.

- At the end of the first pulse, the double pulse test allows to observe "turn-off rated current".

- The current commutates to the freewheeling diode and gets back to the GaN when turning on the second pulse. An oscilloscope properly set will observe "turn-on of rated current" at the rising edge of the second pulse. However, during the turn-on period, the current in the device grows and does so exceeding the rated current. As everything you want to learn takes place during the rising edge, the second pulse can be as short as possible.

- > The important parts are the falling edge of pulse one and the rising edge of pulse two.

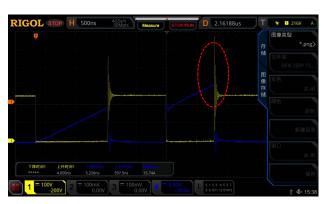

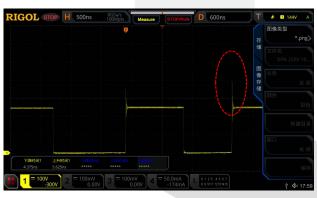

### Double Pulse Tests: Some Tips

- ➤ In DPT, it is important to have a low inductance loop to minimize the V<sub>ds</sub> voltage overshoot.

- For current measurement, a current probe requires additional wiring, which brings high frequency inductance. It is necessary to insert a dynamic current measurement, typically coaxial shunt, into the switching loop.

- ➤ Gate loop is not from the gate drive IC to the device, but from the gate drive decoupling capacitor to gate drive IC and then the device. Magnetic field cancellation concept can be used to minimize the gate loop parasitics.

Double pulse test with additional wiring for current probing

Double pulse test without additional wiring for current probe

A typical coaxial shunt for current sensing

#### Contents

- > Session 1: GaN devices basics

- > GaN, An Introduction

- > GaN Design, Fabrication and Testing

- ➤ GaN Compact Modeling and Reliability

- > Session 2: GaN Gate Driving

- > Session 3: GaN Applications

## Compact Modeling of GaN HEMT

- There are three compact modeling methods: physics-based, semiphysics-based or behavioral model

- The physics-based model is based on the physical structure and internal parameters of GaN HEMT, which is very accurate, however, it's not suitable for power electronics circuit simulations due to the complicated physical parameter extraction process, as well as the long simulation time

- Semiphysics-based model is partly based on the physical structure and internal parameters of GaN HEMT, and some behavioral equations are included

- ➤ Behavioral model is mainly based on behavioral equations of GaN HEMT, the information about the physical structure and the internal parameters of GaN HEMT is not necessary any more

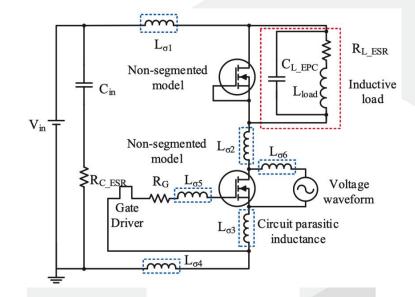

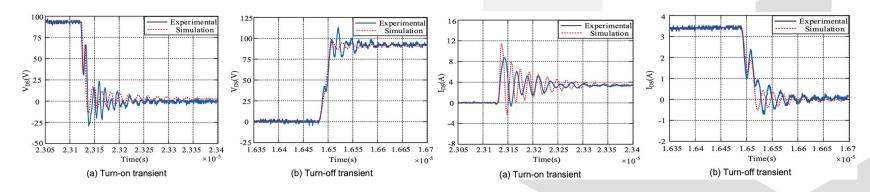

Hong Li, Xingran Zhao, Wenzhe Su, Kai Sun, Trillion Q. Zheng and Xiaojie You; Non-segmented PSpice Circuit Model of GaN HEMT with Simulation Convergence Consideration, IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS 2017

#### Compact Modeling of GaN HEMT: Behavioral model Example

➤ For static modeling that takes temperature into account:

$$\begin{cases} I_{DS} = K_{1}(T) \cdot \ln[1 + \exp\left(\frac{V_{GS} - b_{1}}{c_{1}}\right)] \\ \cdot \frac{(m_{1} + n_{1} \cdot V_{GS})V_{DS}}{1 + P_{1}(T) \cdot (d_{1} + e_{1} \cdot V_{GS})V_{DS}}, V_{DS} > 0 \\ I_{DS} = -K_{2}(T) \cdot \ln[1 + \exp\left(\frac{V_{GD} - b_{2}}{c_{2}}\right)] \end{cases}, V_{DS} > 0 \end{cases} \begin{cases} K_{1}(T) = K_{1} \cdot [1 - l_{1} \cdot (T - 25)] \\ K_{2}(T) = K_{2} \cdot [1 - l_{2} \cdot (T - 25)] \\ P_{1}(T) = [1 - h_{1} \cdot (T - 25)] \\ P_{2}(T) = [1 - h_{2} \cdot (T - 25)] \end{cases}$$

$$\cdot \frac{V_{SD}}{1 + P_{1}(T) \cdot V_{SD}}, V_{DS} \leq 0$$

For dynamic modeling that takes temperature into account:

Model parameters are extracted with measurement data

$$\begin{cases} i_{GD} = s \cdot \frac{1}{1 + \exp\left(\frac{p - V_{GD}}{q}\right)} + r \\ E_{GD} = s \cdot q \cdot \ln[1 + \exp\left(\frac{V_{GD} - p}{q}\right)] + r \cdot V_{GD} \end{cases}$$

Hong Li, Xingran Zhao, Wenzhe Su, Kai Sun, Trillion Q. Zheng and Xiaojie You; Non-segmented PSpice Circuit Model of GaN HEMT with Simulation Convergence Consideration, IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS 2017

#### Compact Modeling of GaN HEMT: Behavioral model Example

- In order to have an accurate simulation, all the parasitics in the circuitry should be included. The numbers can be extracted from either measurements or 3D structural simulations such as Ansoft Q3D:

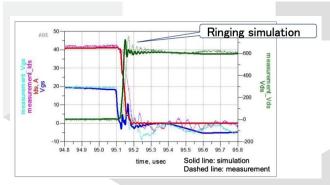

- ➤ Good fits can be obtained from proper parameter extraction for the behavior compact model:

Hong Li, Xingran Zhao, Wenzhe Su, Kai Sun, Trillion Q. Zheng and Xiaojie You; Non-segmented PSpice Circuit Model of GaN HEMT with Simulation Convergence Consideration, IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS 2017

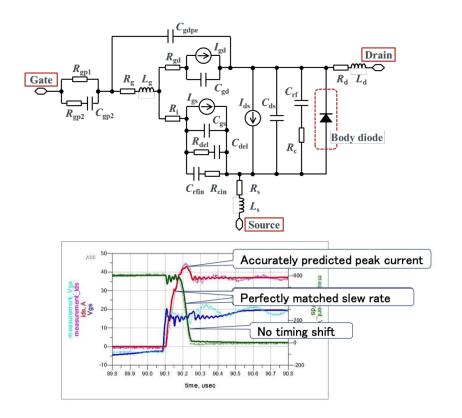

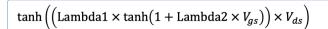

#### Compact Modeling of GaN HEMT: Behavioral model Example

- > Similar modeling method (behavioral model) is also provided by Keysight technologies:

- > Measured device characteristics turned into mathematical representation

- > Accurately represents device behavior which can't be achieved with any physics-based model

- Less parameters with better conversion

- $\triangleright$  Independent of device physics parameters (e.g.  $T_{ox}$ ) → Everyone (e.g. circuit designer) can use

Added Vgs, Vds dependent parameter to drain current equation to better represent unsaturated drain current

$$\begin{aligned} Q_{\rm gs} \\ &= \left( C_{\rm gspi} + C_{\rm gs0} \times \tanh 02 \right) \\ &+ \left( C_{\rm gspi} + \left( C_{\rm gs0} \times \tanh 01 + C_{\rm gs0i} \times \tanh 1i \right) \times \tanh 02 \right) \\ &+ \left( \tanh XX(i) = 1 + \tanh \left( A + B \times V_{\rm gs} + C \times V_{\rm ds} \right) \end{aligned}$$

Added tanhXX to express a positive bias dependence on charge equation

APEC 2018: WBG power circuit simulation with extensive device characterization and modeling Keysight Technologies

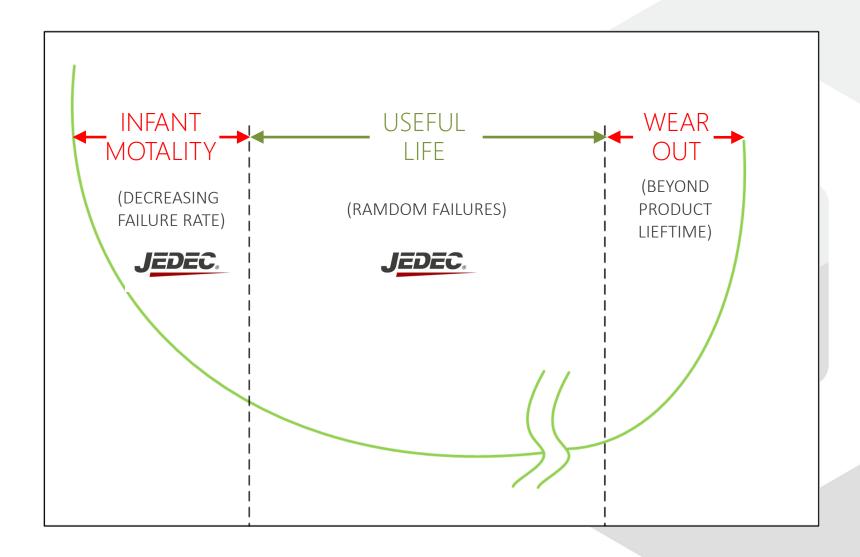

## Reliability Testing: Bathtub Curve

## Reliability Testing: Examples

A typical JEDEC standard reliability tests for power devices should cover a long list of items, here is a highly simplified version to show some of the tested items

| Test Items   | Description                             | Requirements                                            | Number of Chips from 3 lots each |

|--------------|-----------------------------------------|---------------------------------------------------------|----------------------------------|

| HTGB         | High<br>Temperature<br>Gate Bias        | 168h                                                    | 77                               |

| HTRB         | High<br>Temperature<br>Reverse Bias     | 168h                                                    | 77                               |

| Temp. Cycles | Temperature<br>Cycling Tests            | -65°C / +150°C, 500 cycles,<br>dwell time: 10-15minutes | 77                               |

| PCT          | Pressure<br>Cooker Test                 | 96h,T=121°C; RH=100%                                    | 77                               |

| ТНВ          | Temperature,<br>Humidity, Bias<br>Tests | 1000h with bias                                         | 77                               |

| HTS          | High<br>Temperature<br>Storage          | 150°C , 1000hrs                                         | 77                               |

#### Reliability Testing: JC-70

A new JEDEC committee: JC-70 was established in 2017 to deal specifically for wide band gap devices reliability issues. A sample proposed items for guidelines is listed below

#### **REL**

- List of Failure

Mechanisms &

Resulting Failure Mode

- Focusing on Charge Trapping, Charge Injection, Hot Electron, Corrosion, TDDB Like Mechanism, Delam

- Corresponding Acceleration & Stress Procedure

#### **Test**

- Dynamic R<sub>DS</sub>(ON)

- Thermal Resistance (only for cascodes)

- Safe Operating Area (SOA)

#### **Datasheet**

- Include effect of Dynamic R<sub>DS</sub>(ON)

- Nomenclature of parameters to adjust for uniqueness of GaN power transistors

- Transistor circuit symbol to reflect distinctive operation GaN HEMTs

Update: JEP173: Dynamic On-Resistance Test Method Guidelines for GaN HEMT Based Power Conversion Devices was released in 2019

Status of wide bandgap device qualification standards effort by new JEDEC committee JC70, APEC 2018

#### ISO, RoHS and IATF16949

Chemical Laboratory - Kao., SGS Taiwan Ltd.

Test Report No.: KA/2018/A0678

Date: 2018/10/16

Page: 1 of 14

SUMITOMO BAKELITE (TAIWAN) CO., LTD.

NO. 1, HWA SYI RD., TA FA INDUSTRIAL DISTRICT, TA LIAO, KAOHSIUNG, TAIWAN

The following sample(s) was/were submitted and identified by/on behalf of the applicant as :

Sample Description

: EPOXY MOLDING COMPOUND

Style/Item No.

: EME-G700H TYPE A SERIES (LOT NUMBER:8073202)

Sample Receiving Date

: 2018/10/09 TO 2018/10/16

Testing Period Sample Submitted By

: SUMITOMO BAKELITE (TAIWAN) CO., LTD

#### **Test Requested**

(1) As specified by client, with reference to RoHS 2011/65/EU Annex II and amending Directive (EU) 2015/863 to determine Cadmium, Lead, Mercury, Cr(VI), PBBs, PBDEs, DBP, BBP, DEHP, DIBP contents in the submitted

(2) Please refer to next pages for the other item(s).

#### Test Result(s)

: Please refer to next page(s).

(1) Based on the performed tests on submitted samples, the test results of Cadmium, Lead, Mercury, Cr(VI), PBBs, PBDEs, DBP, BBP, DEHP, DIBP comply with the limits as set by RoHS and amending Directive (EU) 2015/863.

An example of RoHS test certificate

- > ISO is the basic requirement for semiconductor manufactures and packaging houses.

- > RoHS (Restriction of Hazardous Substances) is generally required.

- > IATE16949 is one of the automotive industry's most widely used international standards for quality management

- > For fabless design house such GaNPower, we rely on our foundry and packaging partners for these certificates

#### **THANKS FOR WATCHING!**

#### Contact us ( Vancouver Headquarters ):

- 230-3410 LOUGHEED HWY VANCOUVER, BC, V5M 2A4 CANADALGA

- 1.778.588.1119

- information@iganpower.com

#### 联系我们 (Greater China Region)

- 中国江苏省苏州市工业园区纳米技术国家大学科技园F0411

- +86-512-65267027

- sales@iganpower.com

WWW.IGANPOWER.COM 230-3410 LOUGHEED HWY VANCOUVER, BC, V5M 2A4 CANADA