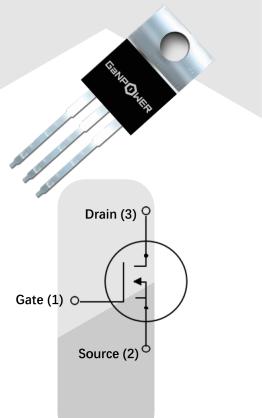

# GPI65030TOL

N-channel 650V 30A GaN Power HEMT in TO220 Package

#### Datasheet version: 2.1

#### **Features**

| BV <sub>dss</sub> | R <sub>dson</sub> | l <sub>ds</sub> | Qg      |

|-------------------|-------------------|-----------------|---------|

| 650 V             | 55 mΩ             | 30 A            | 5.36 nC |

- Ultra-low RDS(on)

- High dv/dt capability

- Extremely low input capacitance

- Zero Qrr

- Outstanding switching performance

- Low Profile

#### **Applications**

- Switching Power Applications

- Server and Telecom Power Applications

- EV OBC and DC-DC Converters

#### **Description**

These devices are N-channel 650 V Power GaN HEMTs based on proprietary E-mode GaN on silicon technology. The resulting product has extremely low on state resistance, very low input capacitance and zero reverse recovery charge making it especially suitable for applications which require superior power density, ultra-high switching frequency and outstanding efficiency.

# **Device Characteristics**

| Static Parameters     |                     |                                                         |                                              | Test data |         |     |      |

|-----------------------|---------------------|---------------------------------------------------------|----------------------------------------------|-----------|---------|-----|------|

|                       | Parameters          |                                                         | Conditions                                   | Min       | Typical | Max | Unit |

| 1                     | V <sub>gs(TH)</sub> | Gate threshold voltage                                  | V <sub>ds</sub> =V <sub>gs</sub><br>Id=3.5mA | 1.0       | 1.2     | 1.4 | V    |

| 2                     | BV <sub>dss</sub>   | Drain-Source breakdown voltage                          | V <sub>gs</sub> =0V<br>I <sub>d</sub> =25uA  |           | 650     |     | V    |

| 3                     | l <sub>dss</sub>    | Zero gate voltage drain current, $T_c$ = 25 $C^{\circ}$ | V <sub>gs</sub> =0V<br>V <sub>ds</sub> =650V |           | 1.5     | 40  | uA   |

| 4                     | l <sub>gss</sub>    | Gate-Source Leakage                                     | V <sub>gs</sub> = 6V<br>V <sub>ds</sub> =0V  |           | 100     | 150 | uA   |

| 5                     | R <sub>dson</sub>   | Static drain-source on resistance, $T_c = 25C^{\circ}$  | V <sub>gs</sub> =6V<br>I <sub>d</sub> =2.5A  |           | 55      | 65  | mΩ   |

| 6                     | $V_{sd}$            | Reverse conduction voltage                              | I <sub>sd</sub> =1A<br>V <sub>gs</sub> =0V   | 1.65      | 1.85    | 2.0 | V    |

| 7                     | R <sub>g</sub>      | Gate resistance                                         | f=25Mhz<br>Open drain                        |           | 1.25    |     | Ω    |

| Dyr                   | namic Paramet       | ers                                                     |                                              | Test data |         |     |      |

|                       | Parameters          |                                                         | Conditions                                   | Min       | Typical | Max | Unit |

|                       | C <sub>iss</sub>    | Input capacitance                                       | V <sub>gs</sub> =0V                          |           | 236     |     | pf   |

| 1                     | Coss                | Output capacitance                                      | V <sub>ds</sub> =400V                        |           | 57      |     | pf   |

|                       | C <sub>rss</sub>    | Reverse transfer capacitance                            | f=1MHz                                       |           | 8       |     | pf   |

|                       | Qg                  | Gate charge                                             | V <sub>ds</sub> =400V                        |           | 5.36    |     | nC   |

| 3                     | Q <sub>gs</sub>     | Gate to source charge                                   | I <sub>d</sub> =7.5A                         |           | 1.2     |     | nC   |

|                       | Q <sub>gd</sub>     | Gate to drain charge                                    | V <sub>gs</sub> =6V                          |           | 1.6     |     | nC   |

| 2                     | Qrr                 | Reverse recovery charge                                 |                                              |           | 0       |     | nC   |

| Switching Performance |                     |                                                         | Test data                                    |           |         |     |      |

|                       | Parameters          |                                                         | Conditions                                   | Min       | Typical | Max | Unit |

| 1                     | t <sub>d(on)</sub>  | Turn-on delay time                                      | V <sub>ds</sub> =400V                        |           | 7       |     | ns   |

| 2                     | tr                  | Rise time                                               | I <sub>d</sub> =2.5A                         |           | 14      |     | ns   |

|                       | t <sub>d(off)</sub> | Turn-off delay time                                     | R <sub>g</sub> =10Ω                          |           | 18      |     | ns   |

| 3                     | La(ott)             | rann on delay time                                      |                                              |           |         |     |      |

# Absolute Max. Ratings

|   | Symbols                | Parameters                                                      | Value       | Unit |

|---|------------------------|-----------------------------------------------------------------|-------------|------|

| 1 | V <sub>DS-max</sub>    | Breakdown voltage transient @ T <sub>case</sub> =25°C           | 800         | V    |

| 2 | $V_{GS-max}$           | Gate to source max. transient voltage @ T <sub>case</sub> =25°C | -12 to +7.5 | V    |

| 3 | I <sub>ds-max</sub>    | Drain to source DC current @ T <sub>case</sub> =25°C            | 30          | А    |

| 4 | I <sub>ds-max</sub>    | Drain to source DC current @ T <sub>case</sub> =100°C           | 25          | А    |

| 5 | dv/dt- <sub>max</sub>  | Drain to source voltage slew rate                               | 200         | V/nS |

| 6 | T <sub>J-max</sub>     | Max junction temperature                                        | 150         | °C   |

| 7 | T <sub>S-storage</sub> | Storage temperature                                             | -55 to 150  | °C   |

# Thermal and Soldering Characteristics (Typical)

|   | Symbols      | Parameters                               | Value | Unit  |

|---|--------------|------------------------------------------|-------|-------|

| 1 | $R_{thJC}$   | Thermal resistance (junction to case)    | 0.9   | °C /W |

| 2 | $R_{thJA}$   | Thermal resistance (junction to ambient) | 60    | °C /W |

| 2 | $T_{solder}$ | Reflow soldering temperature             | 260   | °C    |

# **Ordering**

| Order Code  | Package Type | Packaging Method | Qty |

|-------------|--------------|------------------|-----|

| GPI65030TOL | TO-220-3     |                  |     |

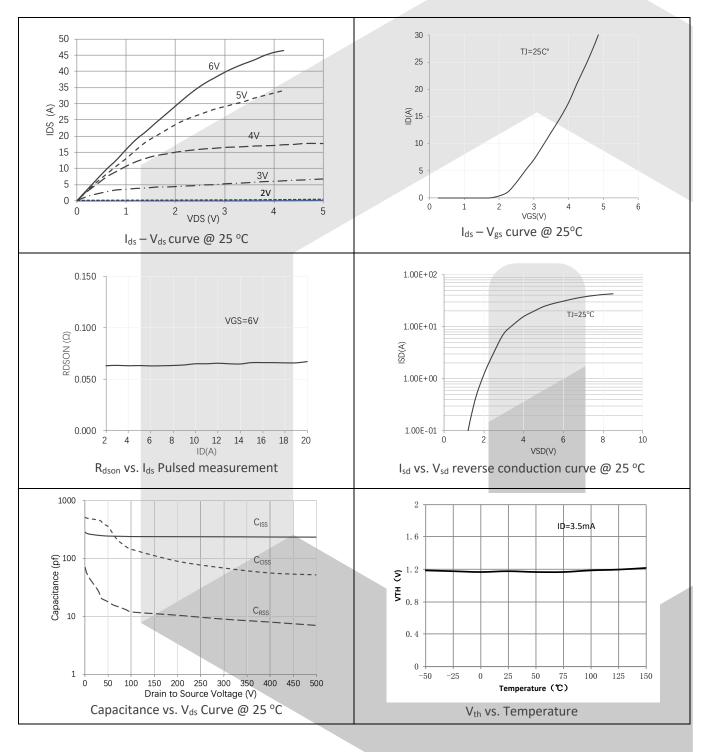

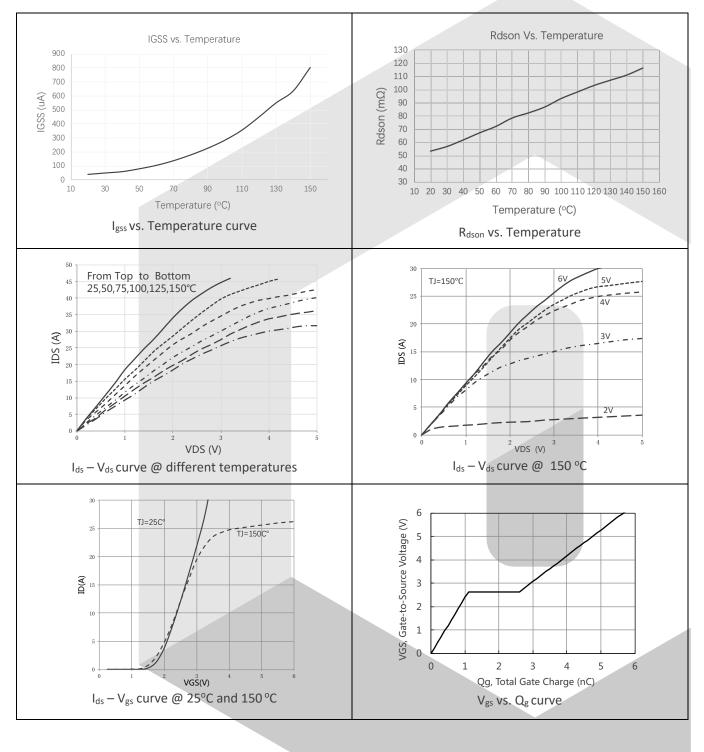

# **Electrical Performance**

For more information, visit us at: www.iganpower.com, or contact us at sales@iganpower.com

For more information, visit us at: www.iganpower.com, or contact us at sales@iganpower.com

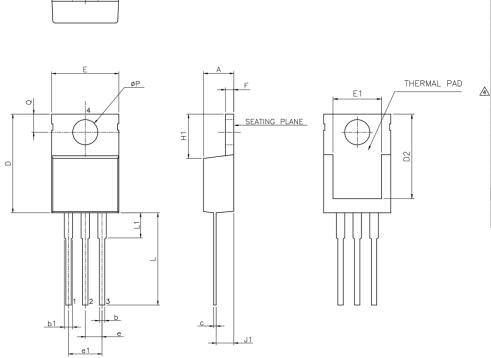

## Package Information

| VARIATIONS | (ALL DIMENSI | ONS SHOWN IN | MM) |

|------------|--------------|--------------|-----|

| SYMBO      | ls MIN       | N. MA        | Х.  |

| A          | 3.5          | 6 4.8        | 32  |

| b1         | 1.1          | 5 1.7        | 7   |

| b          | 0.3          | 8 1.0        | )1  |

| С          | 0.3          | 5 0.6        | 51  |

| D          | 14.2         | 23 16.       | 51  |

| E          | 9.6          | 6 10.        | 66  |

| D2         | 11.7         | 75 11.       | 90  |

| E1         | 6.8          | 6 8.9        | 0   |

| e          | 2.2          | 9 2.7        | '9  |

| e1         | 4.8          | 3 5.3        | 3   |

| F          | 0.5          | 1 1.3        | 9   |

| H1         | 5.8          | 5 6.8        | 5   |

| J1         | 2.0          | 4 2.9        | 2   |

| L          | 12.7         | 0 14.7       | 73  |

| ØР         | 3.5          | 4 4.C        | 8   |

| Q          | 2.5          | 4 3.4        | -2  |

| L1         | 3.6          | 5 6.3        | 5   |

|            |              |              |     |

NOTES: 1. JEDEC OUTLINE : N/A.

#### **GaN HEMT Frequently Asked Questions**

| 1 | Q: Can we do pin to pin switch for silicon MOSFET or IGBT?                                        |  |  |  |  |

|---|---------------------------------------------------------------------------------------------------|--|--|--|--|

|   | A: The short answer is no. GaN HEMT power devices are far superior than the best silicon          |  |  |  |  |

|   | devices such as super junction MOSFETs. However, due to different requirements of gate            |  |  |  |  |

|   | driving voltage and extremely high dv/dt slew rate, special drivers and optimized PCB layouts     |  |  |  |  |

|   | are recommended to minimize the impact from circuit parasitics. Some packaging forms such         |  |  |  |  |

|   | as GaNPower's DFN packaged devices offer both sense and force for the source terminal. Also,      |  |  |  |  |

|   | for traditional TO220 packages, please be advised that the pins are arranged as Gate – Source     |  |  |  |  |

|   | -Drain, and the thermal pad is connected to the source instead of drain.                          |  |  |  |  |

| 2 | Q: Are GaN power devices reliable?                                                                |  |  |  |  |

|   | A: GaN power HEMTs have been tested by GaNPower and many other vendors, users and                 |  |  |  |  |

|   | testing facilities to be as reliable (if not better than) silicon counterparts.                   |  |  |  |  |

| 3 | Q: How do GaN power devices compare with SiC?                                                     |  |  |  |  |

|   | A: Currently GaN power HEMT devices are most suitable for low to medium voltage (≤1200V)          |  |  |  |  |

|   | and power (<20KW) applications. GaN is the ideal choice for high frequency applications. SiC      |  |  |  |  |

|   | devices are better choice for high voltage and high-power applications (>20KW).                   |  |  |  |  |

| 4 | Q: Do we need to parallel an FRD for applications such as inverters?                              |  |  |  |  |

|   | A: GaN devices are different from silicon MOSFET or IGBT in that they have no inherent PN         |  |  |  |  |

|   | junction diodes that cause reverse recovery issue. User do not need to parallel an FRD for the    |  |  |  |  |

|   | purpose of suppressing the body diode reverse recovery effect, since GaN HEMT can operate         |  |  |  |  |

|   | in both first and third quadrants. However, care should be taken for the dead time power loss     |  |  |  |  |

|   | since the Vsd voltage of GaN HEMT is usually close to 2V. This is especially true when a negative |  |  |  |  |

|   | gate voltage is applied.                                                                          |  |  |  |  |

| 6 | Q: Can we parallel GaN HEMT devices?                                                              |  |  |  |  |

|   | A: Yes, GaN HEMT is ideal for paralleling, due to positive temperature coefficient of Rdson       |  |  |  |  |

|   | and slightly positive temperature coefficient of threshold voltage.                               |  |  |  |  |

| 5 | Q: Where can we find drivers for GaNPower HEMT devices?                                           |  |  |  |  |

|   | A: While some of the GaNPower's HEMTs are either monolithically integrated with gate              |  |  |  |  |

|   | driver or co-packaged with a silicon driver, drivers can be easily found from vendors such as     |  |  |  |  |

|   | TI and Silicon Lab for either single sided or half-bridge configurations:                         |  |  |  |  |

|   | ✓ <u>TI: LM5114</u> : Single 7.6A Peak Current Low-Side Gate Driver                               |  |  |  |  |

|   | ✓ <u>TI: UCC27611</u> : 5V, 4A/6A Low Side GaN Driver                                             |  |  |  |  |

|   | ✓ Maxim: MAX5048C: 7A Sink/3A Source Current, 8ns, SOT23, MOSFET Drive                            |  |  |  |  |

|   | ✓ Fairchild: FAN3122: Single 9-A High-Speed, Low-Side Gate Driver                                 |  |  |  |  |

|   | ✓ <u>Silicon Lab: Si827X</u> : 4 Amp ISO driver with High Transient (dv/dt) Immunity              |  |  |  |  |